扫码打开虎嗅APP

本文来自微信公众号: 芯思想(ID:ChipInsights),作者:赵元闯,原文标题:《EDA浪潮(DAC40周年总结)——伯克利大学Alberto教授DAC2003主旨报告分享》,头图来自:视觉中国

DAC 2023将于7月9-13日在美国旧金山召开,加州大学伯克利分校(UC Berkeley)教授Alberto Sangiovanni-Vincentelli(阿尔伯特·桑乔瓦尼·温琴泰利)将再次应邀发表《Corsi e Ricorsi: Here We Go Again》主旨报告。之前,Alberto教授已经在DAC 2003和DAC 2013做过主旨报告。

20年前,Alberto教授应邀在DAC 2003年发表主旨报告《The Tides of EDA》。在报告中,Alberto教授认为半导体和系统设计以及设计自动化是通过一种重复的模式发展起来的,这种模式包括直观的见解、伟大的洞察和严谨的方法,称之为“Corsi e Ricorsi”;并使用了哲学家Giovanni Battista Vico的原则,将EDA近40年的历史划分为“众神时代、黄金时代 、人类时代”等三个时代。

从报告题目来理解,DAC 2023报告应该是Alberto教授20年前在DAC 2003主旨报告的延续。在聆听《Corsi e Ricorsi: Here We Go Again》报告前,让我们先回味一下DAC2003的主旨报告《The Tides of EDA》的精彩内容!

以下是Alberto在DAC2003的演讲内容分享。

图片来自:DAC

我很荣幸,能够在DAC(设计自动化大会)40周年之际参加主题演讲,讲述如何看待40年来DAC相关的研究成果,并阐述EDA(电子设计自动化)未来的趋势和挑战。查找DAC的相关文献资料,确实是一项艰巨的任务。在查找文献资料的过程中,我也在思索,怎么讲述 EDA的历史及其规则模式。我曾是意大利一所古典学院的学生(Alberto教授毕业于米兰理工大学),我在我的同胞、哲学家Giovanni Battista Vico的代表作《Scientia Nova》中寻找到了答案。Vico将人类历史划分为三个时代:众神时代、英雄时代和人类时代。

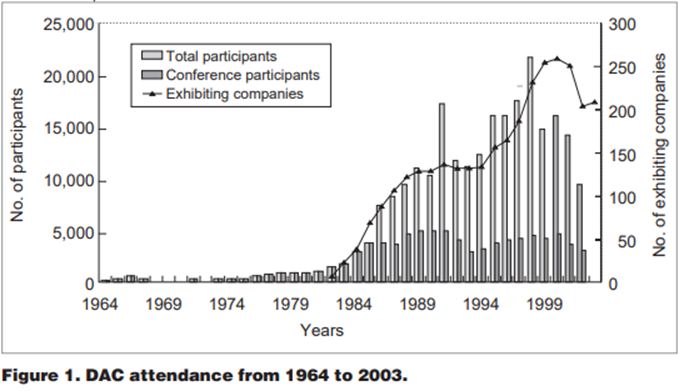

首先,Alberto使用了DAC的参会人员的数据,来识别EDA年代。如上图(Figure 1)所示,可以看到从1964年到1978年的最初时期,那时的参会人员相当稀少;接下来是1979年至1992年的繁荣时期,参会人员急剧增加;最后,从1992年到今天(注:指2003年),在过去几年中出现了相对停滞和明显下降。将这三个时期与Vico所描绘的众神、英雄和人类时代联系起来似乎很自然!

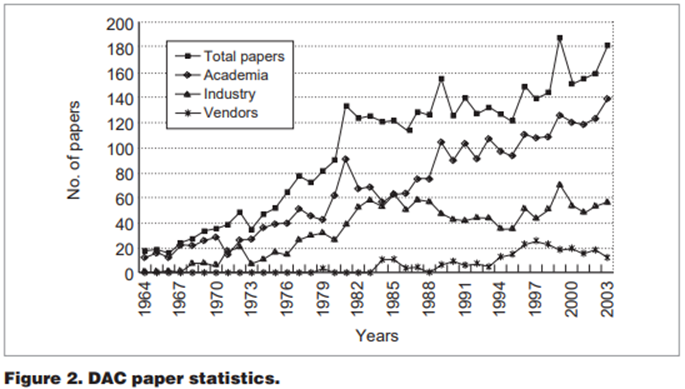

然后,Alberto使用了另一组有趣的统计数据,如上图(Figure 2)所示,就是DAC的论文提交及其来源,众神时代对应着行业论文的盛行;英雄时代,学术论文显著增多;而人类时代,学术论文占据主导地位。

在行业先驱的努力下,这个时代的许多开创性工作奠定了EDA的基础。一些具有开创性的论文,至今仍有着强大而深刻的影响力。这个时代的基础性的成果可以分为五个方面:电路仿真(circuit simulation)、逻辑仿真与测试(logic simulation and testing)、MOS时序仿真(MOS timing simulation)、布线(wire routing)、规则阵列(regular arrays)。

电路仿真。电路仿真一直是DAC的一个非常重要的内容板块,尤其是涉及到IC设计方面。电路仿真在集成电路设计中的巨大成功,是EDA产业诞生的主导因素。IBM的研究人员是这个阶段最突出的力量:Frank Branin是电路仿真的先驱,他确定电路仿真体系结构,Robert Brayton、Gary Hachtel和位于约克镇的IBM T.J. Watson研究中心的同事们在这一领域也做出了基础性、革命性的贡献:他们提出了今天所知的电路仿真背后的算法,从稀疏矩阵(sparse matrices)到向后微分公式(backward differentiation formulae)。他们推动了两个重要项目的开发:IBM的ASTAP(Advanced Statistical Analysis Program)和加州大学伯克利分校的SPICE(电路仿真)。加州大学伯克利分校的Ron Rohrer和Don Pederson做了极其重要的工作,他们的早期贡献使SPICE多年来成为电路仿真的主力军。

逻辑仿真和测试。DAC会议开始前,逻辑仿真已经使用了一段时间。计算机公司,如IBM和CDC,依靠这项技术来调试他们的逻辑设计。这一领域的贡献数不胜数。该领域的创始人在开发自动测试向量生成(ATPG, automatic test pattern generation)与故障仿真(fault simulation)的发展中也发挥了基础性作用。诸如密歇根大学(U Michigan)的John Hayes、南加州大学(USC)的Melvin Breuer、德州大学奥斯汀分校(UT Austin)的Stephen Szygenda(现在SMU任教)等等,都发挥了难以估量的作用。Tom Williams及其同事发明了一种LSSD(level-sensitive scan design)方法,随后IBM的Paul Roth开发了D算法,改变了计算机硬件的设计方式和测试模式(test pattern)的生成方式。

MOS时序仿真。1975年贝尔实验室(Bell Labs)的Hermann Gummel及其同事首次提出利用MOS晶体管的准单向(quasi-unidirectional)特性来加速电路仿真。Hermann Gummel的直觉是用基于松弛法(relaxation-based)的快速启发式算法来近似求解电路微分方程。他洞察到,当分析数字电路的时序时,只要开关事件能够正确放置,那么准确的波形就显得无关紧要。现今的快速电路仿真仍然是基于这一思想。

布线。我们今天在工具中使用的大多数技术都是基于这一时期获得的结果。1961年IBM研究员C. Y. Lee研发出最早的布线工具maze router,比首届DAC还早,然而Lee maze router却是今天我们使用的大部分布线器的基础。Hightower路线扩展算法(line extension algorithm)可以追溯到1969年,而通道布线(channel routing)的想法来自于伊利诺伊大学厄巴纳-香槟分校(UIUC)的Akihiro Hashimoto和James Stevens在1971年的工作中。

规则阵列。随着大规模集成电路的出现,规则布局模式对减少设计时间的吸引力很强。研究人员开发了门阵列(Gate-array,在IBM称为master slices)和标准单元(standard cell,在IBM为master images)来替代原本的定制版图。在这一时期的IBM和贝尔实验室,自动电路版图集成工具被广泛使用。当年,最早的一个门阵列集成电路只有四个逻辑门。现在回头看看人们已经走过的历程:在40年里,从最初的四个逻辑门,到如今一块芯片上数以十亿计的逻辑门电路,进步是巨大的。

当时,分析师认为CAD(计算机辅助设计)对系统行业,尤其是计算机行业具有战略价值。IBM和其他涉及计算机的公司都非常重视CAD,并且投入了大量资金和资源,这些公司内部CAD部门的工程能力是相当强大。

再来看看DAC会议的论文,可以看到日本计算机和通信系统行业发表了许多论文。这些论文描述了使用工具进行系统设计的统一方法,从而展示了CAD技术在世界范围内的战略价值。

在此期间,第一代CAD公司创立,包括1969年的Applicon、1970年的Calma和1972年的ComputerVision。它们的商业模式侧重于工作站销售,软件只被认为是硬件的附属。在这些第一代CAD公司中,没有一家存活到今天。我们可以确定它们消亡的几个原因:

他们产品的体系结构由定制的硬件和主要用汇编代码编写的复杂软件组成。这种体系结构导致它们很难跟上技术的进步,因为软件在这种工作站上进行移植存在严重的问题,设计新的工作站需要大量的投资,然而它们的销售量又十分有限,难以支撑这样的投资,进一步加剧了这一问题。

客户的产品忠诚度有限,因为客户认为他们的附加值很低。

公司对市场变化和客户需求的了解有限。

这些因素导致了它们完全缺乏创新能力,导致了它们最终的消亡。

令人惊讶的是,在1979年至1993年间,EDA领域的各个方面都出现了爆炸性增长。在这个时代里,从物理验证(physical verification)到布局综合(layout synthesis),从逻辑综合(logic synthesis)到形式验证(formal verification),从系统级设计(system-level design)到硬件加速(hardware acceleration),DAC的论坛和展览充满活力和热情,这是生态健康发展的明显标志。技术领域扩展到了非线性和组合优化、控制、人工智能和逻辑等领域。在寻求新方法和工具的过程中,探索了各种途径。曾有几年,描述专用系统和神经网络的论文占据了会议的主导地位;许多小组讨论了这些方法的潜在影响。然而,今天(注:指2003年),几乎没有什么可以显示它们的影响,我很高兴地报告,DAC2003没有接收这些领域提交的任何论文!

在英雄时代里,创立了最成功的EDA公司,著名的研究小组聘请了大量的EDA领域博士;还有更多的学生想要进入这一领域。

这个时期的成果可以分为六个方面:验证和测试(Verification and testing)、版图(Layout)、逻辑综合(Logic synthesis)、硬件描述语言(Hardware description languages)、硬件加速(Hardware acceleration)、高层次设计(High-level design)。

验证和测试。这一领域包括两个研究主线,一是专注于让电路仿真速度更快,比SPICE快几个数量级;另一种侧重于形式化技术,以证明电路能够正确运行。在第一个领域,Richard Newton、Albert Ruehli和我本人(Alberto教授)研究了基于松弛法(relaxation-based)的技术和混合模式仿真,并在1980年左右得出成果,为现在的快速MOS仿真器奠定了基础。Randal Bryant的工作集中在数字电路的仿真上,其速度比SPICE提高了两个数量级,精度介于电路仿真和逻辑仿真的精度之间。

随着几何形状的缩小,互连的影响越来越大。Jorge Rubinstein和Paul Penfield于1981年提出的互连延迟模型(interconnect delay model)得到了广泛的应用。1988年,卡内基梅隆大学(CMU)的Lawrence Pileggi和老师RonRohrer用他们在AWE(渐进波形估计,asymptotic waveform evaluation)方面取得的成果,于1988年解决了互连仿真(interconnect simulation)的问题。

形式化技术(Formal techniques)最初的目标是回答这么一个问题:两个不同的门电路网络是否有相同的布尔(Boolean)函数。在众神时代,IBM研究员Bahnsen就首次使用了形式验证。1986年,Randy Bryant在二元决策图(Binary Decision Diagrams)方面所做的开创性工作,引进了布尔函数的标准型(canonical form)和非常快速的运行算法,彻底改变了这一领域。1990年代初,Olivier Coudert和Jean Christophe Madre关于使用BDD在FSM(finite-state machine)等价方面的工作,以及Ed Clarke、Ken McMillan、Dave Dill和Bob Kurshan关于模型检查领域的工作,将形式验证提升到了更高的抽象级别。模型检查(Model checking)解决了验证由FSM表示的顺序系统是否满足被描述为在状态和转换上定义的逻辑命题的性质,或者被描述为另一个FSM的问题。

在测试领域,1981年,在IBM研究员Prabhu Goel的指导下,著名的基于D算法的Podem-X算法正式面世。

版图。在表现和基本操作层面,版图的编辑发生了根本性的变化。在前一阶段,设计人员为每个设计步骤使用不同的数据存储库,并执行从一种数据格式到另一种格式的繁琐翻译工作。1980年代初,Arthur Newton在加州大学伯克利分校在Squid、Oct和VEM方面的研究工作以及John Ousterhout在Magic systems上的工作,这些革命性的工作彻底改变了该领域,Arthur Newton和John Ousterhout的研究工作表明,可以拥有统一的数据库和图形用户界面。我再怎么强调这项工作的重要性都不为过。OpenAccess数据库借鉴了Arthur Newton的开创性工作;高级物理设计的一些数据表示是基于John Ousterhout提出的角勾链(cornerstitching)数据结构。

另一个革命性的想法产生于硅编译(silicon compilation)和版图语言(layout languages)的研究工作中。大约在同一时间,几个研究小组对这一领域进行了探索。这些小组分别在麻省理工学院(John Battali)、加州理工大学(Carver Mead团队和他们的Bristle Block硅编译器)和贝尔实验室(Hermann Gummel、Misha Buric及其同事以及L版图语言)。当初的想法是将IC设计与计算机科学中某些理论结合起来。尽管这种方法在理论上很优美、很强大,但当今我们使用的工具中几乎不再使用。

IBM的两位研究员Scott Kirkpatrick和Charles Gelatt把自旋系统(spin systems)的知识用到了这一领域中。1980年,他们和Michelle Vecchi提出了模拟退火法(simulated annealing),以此来解决门阵列版图的问题。这种方法一经公布,就引起了人们对其有效实现和理论性质的大量研究。经过定制的算法被用在了标准单元、宏单元版图以及全局布线上,大多数半导体公司,从英特尔(Intel)到DEC,从摩托罗拉(Motorola)到德州仪器(TI),都使用了由Carl Sechen(注:Alberto教授的博士生)写的TimberWolf系统,用于标准单元版图以及宏单元版图。

在英雄时代,理论计算机科学家对研究布局设计的组合方面也产生了极大的兴趣。麻省理工学院(MIT)的Ronald Rivest和Gerald Pinter关于布线(routing)的工作,以及加州大学伯克利分校Richard Karp在布局布线(placement&routing)的工作,都是非常成功的案例。这是EDA成功吸引其他学术领域参与的一个成功迹象。同时,加州大学伯克利分校的葛守仁(Ernest S. Kuh)工作产生了用于宏单元设计的集成布局系统和用于布局布线的点工具,对该领域产生了重要影响。

逻辑综合。逻辑综合一词出自1979年IBM研究员John Darringer、William Joyner和Louise Trevillyan的一篇重要论文。在这篇论文中,他们使用了基于peephole rule的优化方法,生成门电路级的高效设计表示。这一成果出现后不久,另一种Boolean优化方法也于1981年在IBM问世。IBM的Robert Brayton、Gary Hachtel与加州大学伯克利分校的Arthur Newton以及我本人合作,开发了二级逻辑优化器(two-level logic optimizer)ESPRESSO,以及Yorktown Silicon Compile(YSC)和Multilevel Interactive Synthesis (MIS)两个多级逻辑优化器(multilevel logic optimizers)。

这项工作由美国DARPA支持,历时10多年,在MIS的早期开发中,首先是一个工艺独立(technology-independent)阶段,在这一阶段中Boolean函数被不断调整和优化;随后是一个工艺映射(technology-mapping)阶段,在这一阶段中经过优化的Boolean函数映射到门电路库。英特尔、意法半导体(STM)、德州仪器、摩托罗拉、霍尼韦尔(Honeywell)、DEC和飞利浦(Philips)等大公司都很快采用了该版本MIS。

关于第二阶段工艺映射,通常采用的方法是使用基于规则(rule-based)的技术,比如通用电气(GE)的Aart De Geus(注:Synopsys新思科技创始人、董事长、CEO)及其同事开发的SOCRATES系统就是如此。1982年,当时我本人在普林斯顿大学(Princeton)的一场讨论中遇见Kurt Keutzer,他向我展示了Alfred Aho 和Jeffrey Ullman在编译方面的研究成果--非常高效的工艺映射(technology mapping)。其中采用的想法是,把原问题表示为一个树覆盖(tree-covering)问题,然后用动态规划法来解决它;这是一个非常伟大的想法,目前的绝大多数逻辑综合系统都是基于这一想法。在IBM的John A. Darringer的创新工作的基础上,日本的Fujitsu、NTT以及NEC等公司进行了卓有成效的研究工作,产生了可实际工作的逻辑综合系统。

逻辑综合对于EDA领域来说是一项伟大的成就,产生了大量的论文,同时也吸引了其他相关领域的人们的极大兴趣。我在1985年国际测试大会(International Test Conference)的一次主题演讲中,断言测试模式生成(test pattern generation)和逻辑合成(logic synthesis)是一枚硬币的正反两面。Kurt Keutzer、Srinivas Devadas、Sharad Malik(Robert K. Brayton的博士生)、McGeer和Saldanha与Robert Brayton、Arthur Newton和我本人合作的工作,展示了使用逻辑合成技术(logic synthesis techniques)在冗余去除(redundancy removal)和延迟测试(delay testing)方面的几个结果。Vishwani Agrawal和郑光廷(Kwang-Ting Tim Cheng)等人提出的一些新新测试算法,源于逻辑综合与测试两个领域之间的交叉。

在逻辑综合的成熟时期,Coudert和Madre通过使用BDD,大大加速基于布尔函数CNF(conjunctive normal form)表示的逻辑综合算法。

硬件描述语言。以逻辑合成为特征的技术工作,归类为逻辑优化(logic optimization)更合适,因为算法将数字电路的布尔函数表示转换为优化的等效表示。综合意味着两层抽象之间的桥梁。为了比布尔函数更有效、更简洁地表示数字电路,硬件描述语言于是应运而生。真正的综合工作就是将HDL(Hardware Description Language)描述映射到门的网表(netlist)中。不幸的是,HDL的开发是独立于逻辑优化工作而开始的。这意味着逻辑合成算法不能处理所有的HDL(由Moorby及其同事提出Verilog)和VHDL(Very high speed integrated Hardware Description Language)结构。于是,有必要将这些语言的使用限制在其所谓的“可综合子集(synthesizable subset)”内。尽管HDL在设计周期早期引入验证在减少设计时间方面确实是一个巨大的进步,但对取子集的需求表明HDL在语义方面存在一些问题。

这些年来,HDL之争非常有趣:Verilog HDL是一种专有语言(Gateway Design销售Verilog仿真器并授权使用该语言),而VHDL是DARPA支持的VHSIC计划中的开放标准。在DAC会议上,就这两种语言谁更有优越性,进行过无数次辩论。当Verilog HDL也开放后,仍然有一些人根据自身口味表达了强烈支持其中一种进反对另一种,但两者之间已经不存在什么差异。在DAC1991会议上,Joe Costello(时任Cadence的CEO)非常雄辩地认为,为一项任务采用两个标准通常是个坏主意:“…VHD的使用是EDA历史上最大的错误之一,导致用户和EDA供应商浪费了大量的资金……”

硬件加速。所有EDA方法都要在非常大的数据集上执行复杂的算法,这需要花费大量的计算时间。随着技术的快速扩张,用定制化硬件以加快EDA算法的执行变得极具吸引力。和往常一样,IBM(我认为它是该领域影响最大的机构)由Gregory Pfister及其同事提出了一种用于逻辑仿真、高度并行的专用架构Yorktown Simulation Engine(YSE)。它在性能上的巨大优势,引起了产业界的强烈反应,很多新公司也纷纷瞄准这一市场而建立(注:Quickturn、PiE Design、IKOS都是在这一时期成立。不过,经历了各种合并与收购,今天这些公司已经不复存在)。

硬件加速的想法扩展到了其他EDA领域,包括布线(比如IBM的Ravi Nair和col League)。然而,它在其他领域没有足够的吸引力来复制在YSE上的成功。

在这项工作的同时,研究人员还提出了另一种想法,即使用通用并行计算机来实现类似的性能优势,但开发成本较低。在1980年代末,计算机界对并行体系结构表现出了极大的兴趣。麻省理工学院Danny Hillis设计的大规模并行系统Thinking Machine,在包括EDA学术界和产业界引起了轰动。这期间成立了Thinking Machine公司,旨在推广这种计算方法,以及吸引该领域中最聪明的大脑,如1965年诺贝尔物理奖获得者Richard Feynman在Thinking Machine公司待了很长时间,设计并实现了处理器之间通信的布线算法。当时最杰出的科学家举办了很多关于算法和应用程序的研讨会。研究人员为这种体系结构开发了算法,包括电路和逻辑模拟算法,以及布局和路由算法。然而,公司没有认识到,对于最终的用户来说,完整的解决方案才是最重要的,而不是仅有硬件就行了。这就大大限制了公司产品的工业使用(它只在实验室中有所使用),并最终导致了公司的消亡(注:Thinking Machine公司确实是将科学成就转化为商业的一次精彩的尝试)。

在同一时期,EDA中的其他人积极追求并使用并行体系结构,如Ncube、Sequencet和Intel hypercube。然而,到目前为止,还没有人出售基于这些机器的商业工具。我认为,具有不同程度异构性的并行计算仍然是EDA和其他工程应用的重要结果的未开发来源。然而,在并行计算得到广泛应用之前,研究人员必须解决软件支持的根本问题。

高层次设计。高层次或系统级设计是一座通往未来的桥梁。当时的研究者都同意,提高抽象水平对于将设计生产力提高几个数量级至关重要。我确实对这个领域充满热情,我相信我们的未来取决于该领域设计方法和工具的成功。在1980年代,一些高层次综合的基础性研究工作已经展开(诸如Thomas、Parker和Daniel D. Gajski)。这项工作几乎与逻辑综合并行开始,研究人员开发了几种商业工具。尽管如此,设计界并没有广泛接受,还有许多工作要做。

最根本的问题是,为何逻辑综合能够成功,而高层次综合的推广如此困难?我本人认为,最初的高层次综合工作过于笼统;设计师们不得不寻求太多的替代品,而这些工具暂时很难击败人类。然而,当系统级设计侧重于受约束的体系结构,如DSP和基于微处理器的体系结构时,高层次综合在工业上取得了一定程度的成功。IMEC的Hugo De Man(IMEC的创始人,Don Pederson的学生)和学生Jan M. Rabaey在Cathedra系统方面的工作,就是在这一狭窄领域取得成功的一个好的例子。硬件-软件代码设计方法嵌入系统包括斯坦福大学(Stanford U)的Vulcan、布伦瑞克大学(Braunschweig University)的Flex(Paulin、Cosyma开发)和加州大学伯克利分校的Polis。

在此期间,Ed Lee开发了Ptolemy,David Harel开发了Statecharts,用于算法层面的设计捕获和验证;这项工作影响了现有的嵌入式系统设计方法。在软件设计方面,INRIA的Gerard Berry和Albert Benveniste以及Verimag的Paul Caspi和同事提出了同步语言(Esterel、Signal和Lustre)。

在英雄时代,EDA研究成为人们关注的焦点,在电气工程和计算机科学领域同样受到关注。这项工作的相关性在EDA研究人员收集的许多奖项以及以下惊人的统计数据中变得显而易见:根据Citeeer数据库,被引用最多的三篇来自EDA的论文分别是:

“Optimization by Simulated Annealing模拟退火优化”, Scott Kirkpatrick等人,1983年;

“Graph-Based Manipulation of Boolean Functions基于图的布尔函数操作”, Randal E. Bryant,1986

“Statecharts: a Visual Formalism for Complex Systems状态图:复杂系统的视觉形式主义”, David Harel,1987年。

你可能会说,这些数据并没有显示出科学的卓越性,而是EDA领域在引用他人的工作时比其他更传统的计算机科学领域更慷慨。但无论如何,我认为频繁引用是一个积极的方面。

第二代和第三代EDA公司就是在这一时期创立的。第二代公司Daisy、Mentor和Valid成立于1980年至1981年,为数字设计市场提供原理图数据采集和工作站模拟服务。Daisy和Valid采用了第一代公司的传统方法建立自己的工作站。相比之下,Mentor出售Apollo工作站时附带了原始设备制造商协议。硬件销售占这三家公司收入的很大一部分。

1982年和1983年, ECAD(黄炎松Paul Huang创立)和SDA成立了,并于1988年合并成立了Cadence。这些公司是纯软件公司的第一个例子。因为我本人参与了SDA的创立,我想分享一个你们很多人可能不知道的花絮。ECAD和SDA实际上从一开始就应该是一家公司,但黄炎松这时已经研发完成了他的物理设计验证系统Dracula,并想要快速投入市场,然而SDA方面尚未准备妥当,于是便分成两家。SDA早在1987年就准备在投资者仍称之为“黑色星期一”的那一天(指1987年10月19日)上市。之后的几个季度里,股市状况依然相当糟糕。因此,黄炎松、Joe Costello、Jim Solomon和Glen Antle认为,最好的办法是通过与ECAD的合并将SDA上市,合并后的公司名为Cadence。

在此期间,围绕着硅编译(silicon compilation)和符号版图(symbolic layout)的概念,成立了Silicon Compilers和Silicon Design Labs。ViewLogic从PC的角度追求EDA市场,旨在为数字设计提供低成本的解决方案,成立了Gateway,将Verilog及其相关模拟器商业化。

1987年,Optimal Solutions Inc.在北卡罗来纳州成立。没有多少人知道这是Synopsys的原名!很明显,比较一下利润率的差异就会发现,销售工作站硬件并不是一个很有吸引力的商业模式。不过直到1990年,EDA界的知名人士(应该是时任Mento的董事长De Bruggere)对“纯软件”公司的商业模式发表了负面评论,称如果不销售工作站硬件,没有办法支持一家长期成功的EDA公司。专业的硬件加速公司也在这一时期成立:Quickturn、PiE Design和IKOS等。不过,经历了各种合并与收购,今天我们已经无法见到一家独立的硬件加速公司。

对于很多IC和系统公司,即使它们有强烈的动机去采用商业的解决方案,但是由于EDA的战略价值,它们在内部进行了大量相关的投资。尤其是贝尔实验室和IBM,它们在EDA工具和环境的竞争中处于领先地位。

在接下来的几年里,由于通用工作站的主导地位,第二代商业模式(硬件加软件)被证明是不可持续的。Daisy和Valid在收购中慢慢死去,而Mentor则重塑了自己,维持市场竞争力。Silicon Compilers和Silicon Design Labs也在一系列并购中消失。Silicon Compilers在其基本形式上,就没有对性能和最终结果给予足够的关注;而版图语言(layout languages)和符号版图系统(symbolic layout systems)也并没有被广泛接受,设计者们已经习惯了用图像和几何来表示他们的设计。

我认为,1993年是EDA领域一个新阶段的开始。技术创新的步伐开始放缓。从华尔街的角度来看,产业界已经成熟,从而更加关注利润,越来越不敢于承担风险。我引用我的同事和朋友Richard Newton在DAC1995主题演讲中的一句话:“今天我想在这里提出的一点是,无论是在工业界还是学术界,我们这门学科都没有承担足够的风险(If there is a single point I wish to make here today, it is that as a discipline, both in industry and in academia, we are just not taking enough risks today.)。”

这一时期恰逢互联网及其应用程序的爆炸式发展。新兴的互联网正在吸引着电气工程(electrical engineering)和计算机科学(computer science)领域最优秀的人才;互联网还吸引了大量风险投资,这种情况自然导致EDA创新率降低。与此同时,半导体行业继续按照摩尔定律推动技术发展,增加了EDA面临的技术挑战。片上系统(SoC)开始吸引人们的目光。

SoC对不同的人来说意义重大,可以意味着很多不同的东西。在日本和韩国,SoC意味着存储器和微处理器的集成;在其他地方,任何使用大量晶体管的东西都可以被称为SoC。在我看来,SoC就是将不同的设计方式整合成一个连贯的整体。跨学科的方法对于解决电子技术进步带来的复杂问题是必不可少的。

相关贡献。对于这一时期的基本贡献,评审委员会仍然没有定论。根据这一时期的特点,我不想在这里把各种研究方法称为成功或失败(现在说还为时过早),而是简单地评论一些重要的话题。我将把确定关键贡献的任务留给10年后发表主旨报告的演讲者(注:DAC2013,Alberto教授再次应邀发表主旨报告,也没有特别提及相关贡献)!

随着几何结构向亚微米范围发展,物理验证(Physical verification)引起了人们的广泛关注。自测试(self-test)成为解决测试设备成本和要求不断上升的唯一解决方案。研究人员研究了异步设计方法和相关的综合问题,作为功率消耗限制和布线延迟不可预测性引起的性能问题的潜在解决方案。有兴趣突破极限(pushing the envelope)的设计师们仍在努力应对深亚微米模式的变化,寻求其极限,以及获得的收益和风险是否匹配。随着芯片包含越来越多的功能,模拟设计已成为瓶颈。在SoC中,最重要的事情就是寻找模拟和数字器件之间的最佳匹配,而不是将模拟部分的性能优化到极致。由于模拟电路对二阶效应的依赖性,使得模拟设计更多地是一门艺术而非科学(more a craft than a science)。我认为,我们必须将科学纳入其中,使这一活动具有可重复性,并比今天快得多。

当布线延迟在芯片设计中变得重要时,实现逻辑合成和版图分离开始成为设计中的问题。也就是说,电路在逻辑级设计时要满足时序约束(timing constraints),在最终布局后仍要满足原来的约束。显然,未能实现设计收敛(design closure)会产生无法接受的上市时间延迟和成本。今天提出的解决方案是将布局和逻辑合成合并到一个单独的优化循环中。

嵌入式系统设计正朝着越来越丰富的软件解决方案发展。这就引起了人们对软硬件代码设计的强烈兴趣,它通过并行化软硬件开发和减少集成时间来加快设计周期。硬件-软件协同合成还意味着使用高级功能模型来推导详细、优化的软件和硬件实现。请注意这里的综合(synthesis)和编译(compilation)之间的区别:当我使用原始设计的数学表示时,我说的是综合,其中包含对特定实现风格的有限偏见。编译意味着从编程语言到汇编或机器代码的转换。在这种情况下,数学抽象是相同的。

在这种背景下思考,我发现早在1967年,DAC就发表了关于软件设计的论文。那么,我们该如何应对未来?基本的区别在于感兴趣的软件类型。一开始,DAC会议论文涵盖和跨越了各个方面,从建筑(buildings)到结构(structures)、从电子电路到“标准”软件(数据库和航空公司预订软件)。现在的焦点主要集中在嵌入式软件上。

我已经提到了互联网和高科技金融狂潮给EDA行业带来的压力。当时,我每天都接到招聘人员的电话,问我的学生是否有兴趣在一家成熟的EDA公司工作,因为没有足够的人来维持EDA公司的发展。老牌EDA供应商有20%的员工离职,他们被互联网和EDA初创公司抢走了。到1999年,EDA大约有80家初创公司。在此期间,Avanti、Ambit、Magma、Monterey、Get2Chip、Verisity和Verplex等公司开始尝试挑战业界的大玩家(注:这些公司最后都被大玩家收购了)。然而,如果我们看看互联网泡沫破灭后的几年,我们会看到一个迥然不同的景象:IPO成功的公司只是极少数,收购是唯一的退出策略,事实没有那么美好。

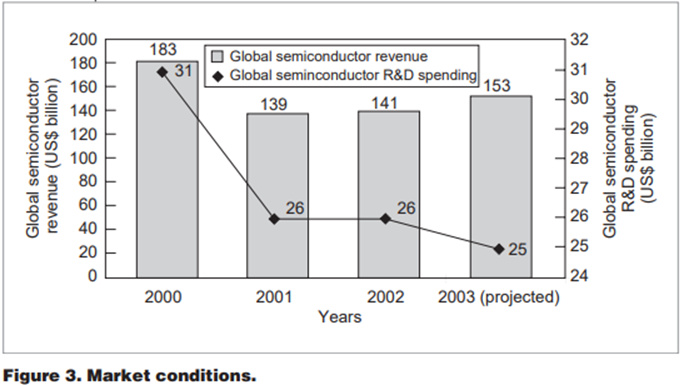

从2000年到2003年这段时间对整个高科技产业来说是非常具有挑战性的。如上图(Figure 3)所示,至少可以说,整体市场状况黯淡;全球半导体研发支出正在减少,因此EDA公司的可用市场总额也在萎缩(根据EDAC的数据,2002年下降了3%)。保持生存和繁荣是一项重大挑战。

与此同时,我们必须对新技术进行创新和投资。EDA必须适应不断变化的商务环境和结构。我们见证了客户与供应商关系的重大变化。随着半导体和系统公司在EDA技术投资上的理性化,伙伴关系变得越来越重要。所有这些都是考虑到半导体技术的根本变化,这需要前所未有的投资规模,同时暴露出当前设计方法和工具的局限性。也难怪许多公司推迟推出其90纳米技术节点。由于NRE(一次性工程费用,non-recurring engineering)和掩模成本,ASIC设计的成本正在迅速上升。新的设计在持续减少,人们转而偏向于使用标准解决方案和软件定制。我们可以根据数据推断出一点:以ASIC为中心的传统EDA市场已经大幅缩水。我们需要重新思考整个设计过程。系统级设计正在主导着未来电子系统新平台的定义。这一趋势在今天并不明显,但在主导设计过程之前,它将变得越来越重要。

EDA除了寻找其他应用领域之外别无选择。EDA的主要客户,半导体公司正在为其产品寻找继PC和手机之后的下一个杀手级应用。

我坚信高科技产业的下一个驱动力将涉及社会的全球利益。人们正在形成一种共识,即电子技术尚未渗透到人们感兴趣的应用领域。这些潜在的应用是社会利益信息技术研究中心的重点,这是一个非常广泛的加州大学项目,以伯克利为中心,由加州大学和工业界赞助。这项研究的核心是由加州大学伯克利分校的Kris Pister和他的同事开发的Smart Dust等设备。Smart Dust将无线通信传感器和信息细化节点结合在一个非常丰富的网络中。

如果我们理所当然地认为这些应用程序将主宰未来的电子领域,那么EDA必须做些什么来支持它们?如前所述,选择的设计风格应该有利于所有形式的重用,并且考虑到NRE和掩码成本的不断增加,使软件比今天更加普及。

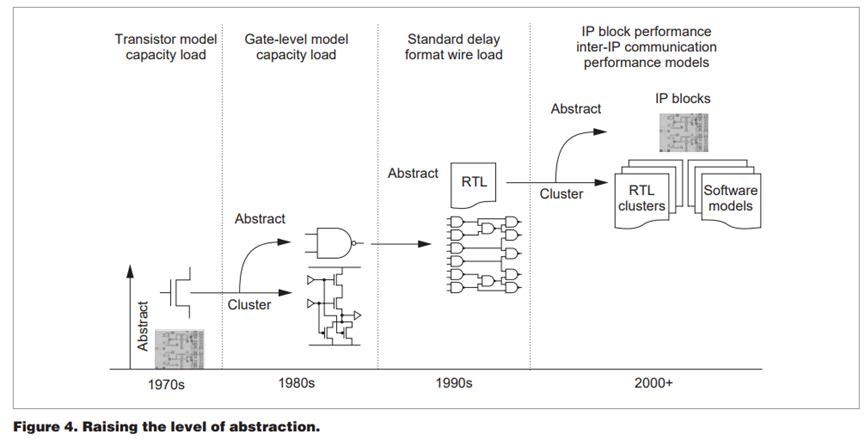

特定通信协议也将在设计过程中发挥重要作用。在设计方法的历史上,设计生产力的变化总是与提高设计捕获的抽象水平有关。1971年(也就是我毕业的那一年),IC抽象的最高水平是晶体管原理图;10年后,IC抽象的最高水平是门阵列。到1990年,HDL已经普及,设计捕获处于寄存器传输级别。下图(Figure 4)显示了抽象级别的这些转换。

在未来,EDA必须使用比现在性能更丰富的块(blocks)来提供所需的生产力提高。我们必须将系统级问题纳入芯片设计。用于描述系统的新语言的出现,如SystemC(由Stan Liao及其同事开创)和System Verilog,清楚地表明了这一趋势。然而,它们未能在更高的抽象级别上解决系统设计问题,主要是因为它们缺乏清晰、明确的综合语义。

我已经谈论这些问题超过15年了,但我仍然对它们充满热情。在这段时间里,趋势很明显:电子行业一直在快速细分。系统公司已经缩减开支,回归其产品规范和细分市场的核心竞争力,并将交付工程和系统组件的任务转移给其他公司。例如,像爱立信(Ericsson)和诺基亚(Nokia)这样的系统公司越来越少参与芯片设计。因此,半导体公司必须为其战略客户做更多的事情。一些工程责任已经移交。与此同时,半导体公司越来越依赖专业公司提供的SIP(Silicon Intellectual Property,硅知识产权),例如ARM用于处理器核心和Artist用于库。一些制造业已经转移到联电(UMC)、IBM和台积电(TSMC)等公司。除了英特尔,这些都是将新技术推向市场的领导者。

在PCB方面,像Solectron和Flextronics这样的专业制造公司占据了制造业的大部分份额。支持这一运动需要将设计视为一项跨越公司边界的高度集成的活动,这项任务绝非易事。

与机械工程和电子、射频(RF)和微机电系统(MEMS)一样重要的工程学科的能力必须成为综合环境的一部分。这样的环境必须提供替代解决方案的经济分析,以及一套能够暴露可用设计中的权衡的工具。EDA必须支持具有严格语义的设计表示,这反过来又支持设计团队之间的干净交接和更稳健的设计验证方法。能够处理设计和制造数据的数据库将不得不出现。我们称这一新兴领域的设计链支持为EDA提供了一个巨大的机会,可以提高其在附加值和经济机会方面的相关性。为了应对这一挑战,我们必须将设计视为一门科学,而不是一套技术。

在我看来,平台是一个“不透明(opaque)”的抽象层,它将下层的关键参数暴露给上层,这是设计链支持设计方法的重要组成部分。我认为基于平台的设计是系统从概念到现实的一系列步骤。逻辑综合是从RTL应用到抽象逻辑门的范例。在这种观点中,我们为实现而限制自己的门的库是较低级别的平台,而RTL描述是顶级的平台。选择最好的实现平台意味着使用库中的门来“覆盖”RTL描述中的逻辑函数。

相反,考虑使用一个公共语义域来表示堆栈中抽象的顶层和底层。在这种情况下,我们总是可以将最佳下层平台的选择作为一个覆盖问题。在我看来,我们的重点一直是“中间”级别,这与ASIC设计方法相对应。我们没有关注顶层(系统级的抽象层)和底层(电路设计)和制造之间的联系。这两层是为设计过程增加价值的最佳机会。

在系统层面,我们应该密切关注嵌入式软件设计,将其视为创新的大好机会。在过去的六年里,DAC的主题演讲指出了软件对电子产品甚至半导体行业的巨大重要性。人们一致认为,需要改变我们设计软件的方式,尤其是嵌入式软件。一些恐怖故事将火星着陆器和阿丽亚娜火箭等非常昂贵的系统的故障归咎于软件错误。此外,Fabio Romeo(时任Magneti Marelli执行副总裁)在DAC2001的主题讨论(Plenary Panel)中介绍了一个关于汽车行业嵌入式软件的有趣统计数据。在他的数据中,嵌入式软件的生产率从每天6到10行代码不等,具体取决于应用程序。这些公司记录了从项目开始到测试结束的生产力指标。然而,即使经过广泛的测试,该软件平均每百万行代码中也有3000个错误。我在走访了不同行业的几家公司后,发现这种情况很常见。嵌入式软件的设计方法必须更多地成为一门科学,并将软件视为一种实现选择,而不是产品的一个孤立方面。

由于嵌入式软件的正确性往往与其时序行为有关,我们必须以某种方式将行为与实现平台联系起来;这意味着一种不同于经典的范式,后者小心地隐藏了计算引擎的细节。我们必须从整体上考虑嵌入式系统的设计,而不是只关注嵌入式软件来解决问题!要做到这一点,教育体系必须改变,拓宽工程专业学生的背景,培养他们将嵌入式系统视为一个整体。我们需要同时而非独立地设计硬件和软件的方法。软件开发人员将不得不处理表征硬件行为的参数。这样做将允许他们预测与软件在实现平台上的执行相关联的物理量;这些数量包括定时、内存占用和功耗。反过来,硬件设计者必须知道什么是应用软件正确工作的重要因素。

特征尺寸的缩小导致电路设计和工艺开发之间的关注点分离。电路设计者不再忽视细节物理效应对制造过程的影响。随着最小特征尺寸缩至低于光波长,掩模制作变得复杂,以描绘光衍射图案。据统计,0.13µm的设计返工率(re-spins)高达50%,令人无法忍受;这在一定程度上推迟了90nm技术节点的广泛采用。这种情况促使我们结合抽象层,以便设计师在电路设计中考虑制造,制造端意识到设计的需求。

然而,正如我之前所说,关注点的分离对于设计生产力和降低错误水平至关重要。因此,基于平台的设计原则在这个级别上也应该是相关的。我们必须确定制造业应该“输出”到设计中的重要参数,以便电路设计者充分意识到他们的选择所带来的影响。设计师还应该将他们需要满足的约束传播到制造层面,以确保设计能够正确工作。DFM(Design for manufacturing)将是半导体行业和EDA行业的重要战场。

我从两个方面概述了EDA面临的巨大挑战。我认为EDA行业必须投入适当的关注,以扩大业务的运营边界,从而拥抱更多的市场。然而,当整体业务形势困难时,它必须这样做。创新是一个代价高昂、风险巨大的命题,有时与中型上市公司的地位相冲突。其结果是我们多年来所看到的:主流EDA公司进行了一波并购。

正如几年前Smith Barney分析师Robert Stern所说,“收购公司是EDA行业进行研发的有效方式。”尽管我同意Robert Stern的观点,但找到更多的创新机制也很重要。创业公司在EDA领域的创新是渐进的,除了少数(尽管很重要)案例;成功的创业公司找到了更好的方法来做我们已经知道如何做的事情。此外,在这种经济环境下,大公司往往在每股收益和资本化方面都优于市场。风险投资在四年内呈下降趋势;IPO窗口于2001年底关闭。从那时到今天,没有一家EDA公司上市。2002年,小型公司的市场份额仅占整个EDA市场的7.8%,而且正在节节败退。大型EDA公司的股价表现与纳斯达克市场一致,但小型EDA公司的股价表现远不如纳斯达克指数。

正如Robert Stern几年前所说,因此,尽管创业概念仍然有效,对于培育创新格局的重要组成部分来说是必要的,但我们需要新的方式来支持大规模创新。我们必须思考如何使创新在老牌公司内部“安全”。。我们必须支持一种模式,即一家老牌公司的财务和商业实力与一家初创公司充满活力的环境相结合。有想法的人必须能够创新,摆脱任何企业环境中典型的日常琐事。他们必须有激励措施和相关的责任感,使成功的动机更高。然而,还需要作出更多的努力。

我认为供应商和客户之间的合作是缓解创新问题的重要途径。它在英雄时代非常有效。例如,我再怎么强调合作伙伴关系对Cadence和Synopsys成功的影响也不为过。创新合作应该包括学术界,形成“良性三角(virtuous triangle)”,这是Hugo De Man首次提出并推广多年。然而,我们在DAC上,还没有看到代表应用领域的系统工程师,也没看到工艺工程师。我们需要共同努力,将这些资源带到DAC,使其成为EDA新时代的论坛。然而,这显然是不够的。一些倡议,如Marco Focus研究中心,将三方聚集在一起,寻找设计电路的新方法,但我认为我们必须走得更远。

我认为,由于资源不断向中国和印度等国家流失,美国在软件和电子系统设计方面肯定有失去领导地位的风险。尽管这种全球资源转移可能被视为积极的,因为降低了成本,提高了盈利能力,但它可能会造成类似于我们在1980年代看到的情况,当时IC制造业正快速从美国转移(IC制造业的份额在几年内从90%暴跌至40%)。当时许多人认为,集成电路制造是一种战略资源,该行业应共同努力改善美国的集成电路制造业,并保持装备行业的经济可行性。

我认为集成电路和电子系统的设计比制造更具战略意义。然而,随着电子系统和软件设计向远东迁移,我们不断失去工作和技术基础。

由于装备制造商对制造业至关重要,EDA对设计业至关重要。考虑到之前的经济条件和行业结构,EDA与1980年代的设备公司处于类似的地位。随着软件编程工作的转移,它使劳动力的智力构成变得贫穷,并大大增加了出现强大竞争对手的可能性。

可以说,SEMATECH通过在困难时期保持创新,在保持IC设计和器件制造业的运营方面发挥了强大的作用。为什么不能在EDA行业建设一个类似SEMATECH模式的EDATech呢?EDA领域对大规模创新的承诺还不够。EDA行业需要一个基础设施来支持对革命性技术的高风险投资。SEMATECH是政府和企业的一项重大努力,为下一代制造线和装备奠定了基础,之前这些生产线和装备面临着缺乏必要资金和投资的风险。这项工作不可能成功地实施这个计划,但必须采取一些措施。要使EDATech这样的举措发挥作用,我们还需要EDA行业以共同的结构共享技术、开发工作和研究。它还必须促进设计师和EDA专业人员之间的合作。

多年来,我注意到EDA领域的设计专业知识显著减少。这种情况的发生当然造成了困难,因为EDA公司不再有能力“发明”新的设计方法,为设计师提供实质性的生产力提高。如今,IC公司高管经常感叹,他们面临着无法利用数十亿美元制造业投资的风险,因为他们缺乏设计方法、工具和流程的适当支持。

EDA是一个独特而精彩的领域。多年来,研究、创新和商业已经融为一体,过去40年的成就证明了这一点。EDA能否继续寻求更好的设计方法,在提高质量的同时,将电子系统设计师的生产力提高几个数量级?我相信是这样,但这不是一条容易的道路。许多困难摆在我们面前。我呼吁增强紧迫感,加强供应商、客户和学术界之间的合作。

最后,我想引用Giovanni Battista Vico的另一句话,我相信这将给我们所有人带来灵感。他将英雄时代描述为“对真理的神圣狂热,生活在超越极限的永恒尝试中,在自我实现的无限可能性中,超越自我,发现精神力量,并向知识提供新的推动力(The holy furor for truth that lives in the eternal attempt to go beyond the limit, in the infinite possibility of self-realization and of overtaking ourselves to discover the power of the spirit and give a new push towards knowledge.)。”让我们努力实现这一点。

本文来自微信公众号:芯思想(ID:ChipInsights),作者:赵元闯