扫码打开虎嗅APP

本文来自微信公众号:半导体行业观察 (ID:icbank),作者:杜芹DQ,题图来自:视觉中国

自1971年英特尔推出第一款 4004 芯片以来,集成电路中的晶体管数量以惊人的速度增长。现在,半导体行业不得不承认,“微芯片上的晶体管数量大约每18个月就会增加一倍”的摩尔定律即将走向终结。仅通过缩小晶体管尺寸来跟上摩尔定律的步伐是不可持续的,维持这种进步速度的成本是天文数字——晶体管密度每增加一倍,就需要资本投资同时增加一倍。而且物理难题也层出不穷。

但是人工智能、5G和数据中心等应用对芯片的需求还在继续,半导体仍要继续发展。行业也并没有放弃摩尔定律,只是每一次的进步都异常艰难。在芯片继续演进的前路上,各路技术齐上阵,展示着各自的实力和潜力,但也有各自的限制和不足。

封装技术

首先出场的是封装技术。封装技术是一支无法忽视的力量。随着大算力需求提升,以及单芯片向更先进制程推进难度的增大,芯片性能的进步更多地依赖于包括封装、测试和组装等生产后端。曾经,封装仅被视为容纳和连接半导体所必需的组件。

如今,先进封装被视为推进半导体技术走向前沿的机会,先进封装的一大优势是它可以增加互连的密度,从而提高信号速度和整体处理能力。这促使企业大力投资先进封装研究和资本。也因此,《先进封装,迎来大爆发》,据Yole预测,高端封装市场在2022年的价值22亿美元,预计到2028年将超160亿美元,2022~2028年的复合年增长率为40%。

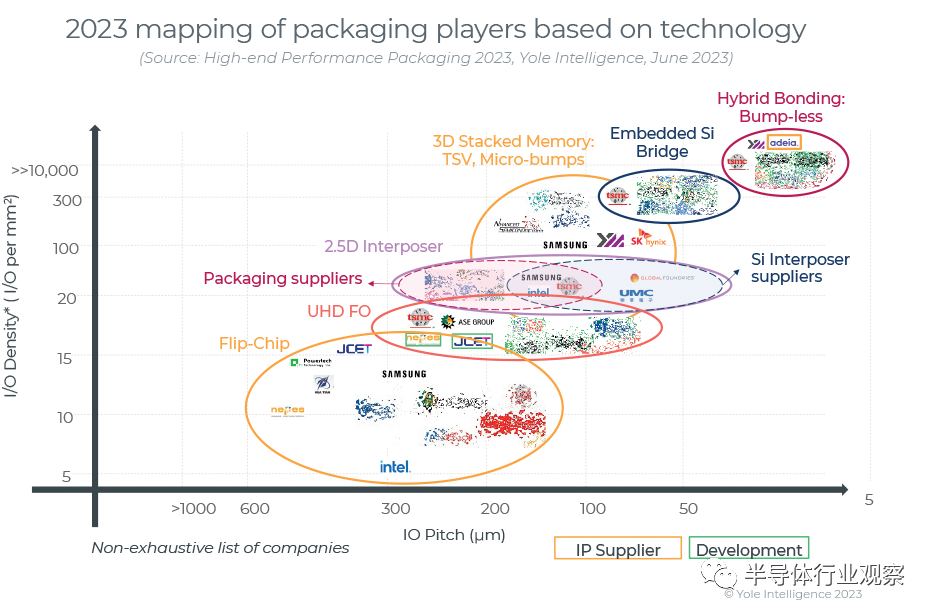

先进封装玩家一览(图源:Yole)

不过顶尖的先进封装技术都掌握在晶圆代工巨头手中,由于先进封装提供了比传统后端封装更高价值的机会,因此主要参与者和快速追随者正在开发各种形式的封装技术并将其商业化,以赢得优质客户。台积电、英特尔和三星是推动先进封装创新的主要参与者。

台积电利用CoWoS、InFO和3D SoIC解决方案提供了3DFabric技术平台。英特尔也积极布局2.5D/3D封装技术,如Foveros、EMIB和Co-EMIB产品,以及后来的Foveros Direct & Omni。三星有I- CubeS 、H-Cube,以及后来的R-Cube和X-Cube等2.5D和3D封装技术。因此,他们之间围绕先进封装的竞争也愈发激烈。

从技术上来看,他们主要在采用硅通孔(Through-Silicon Via, TSV)、模具通孔(Through-Mold Via, TMV)、微凸块和混合键合等技术来减小互连间距。3D封装发展的初期主要是通过裸片上的一个个的小铜凸块来提供芯片之间的垂直互联。凸块的尺寸范围只能从40 µm间距到最终缩小到20 µm或10 µm间距,混合键合技术是实现10µm及以下间距另一个有潜力的连接技术,它使用小型的铜对铜连接来连接封装中的裸片,能够为3D封装提供卓越的互联密度。

除此之外,晶圆代工厂商们甚至开始向封装材料上进击,英特尔于9月18日,对外披露了其半导体玻璃基板技术的开发进展。英特尔认为,有机材料不仅更耗电,且有着膨胀与翘曲等限制,至2030年前,半导体产业很可能会达到使用有机材料在硅封装上延展电晶体数量的极限,玻璃基板将是下一代半导体确实可行且不可或缺的进展。

相较有机基板,玻璃基板具有卓越的机械、物理和光学特性,在单一封装中可连接更多电晶体,提高延展性并能组装更大的系统级封装(SiP)。芯片架构师将能在一个封装上以更小面积封装更多小芯片,同时以更高弹性、更低的总体成本和功耗实现效能和增加密度。

互连技术

“互连”也是芯片技术挑战的重要参与者。曾经,晶体管的速度是制约芯片性能的限制因素,但随着当今动辄数百万晶体管芯片的出现,更多的晶体管使得线路的电阻也随之增加,此外,在间隔非常近的相邻线路之间可能会发生电容耦合。这两者都影响了信号的传输。当下,芯片的计算能力(FLOP)增长速度均快于每一代芯片/封装中输入和输出数据的速度。如今,互连已经成为一大限制因素。

在芯片互连技术上,目前铜互连仍然是行业普遍的做法。1997年,IBM率先从铝互连转向铜布线互连,自那时起,铜一直是用于制造逻辑后端(BEOL)应用中的互连线和通孔的主流导体金属。但随着芯片工艺迈入更先进的工艺,在10nm或更小的尺寸,铜的电阻率急剧增加,从而开始影响电子电路的性能。

于是,行业也早已发起对铜之外的新材料的探寻。研究显示,钴 (Co)、钌 (Ru)、铑 (Rh)、铱 (Ir) 和钼 (Mo)等材料在更小尺寸下具有更好电阻表现。不止如此,像imec这样的研究机构在大约五年前就开始为未来互连应用寻找替代二元和三元合金金属的研究。但是新材料想要替代铜互连,不是易事。

互连不仅包括硬件层面的物理互连,还包括更高层次的接口和协议技术(如不同设备或系统之间的通信接口和标准)。如PCIe、以太网、NVMe、Linux、TCP/IP、RDMA这些接口技术都在互连方面发挥着重要的作用。近些年来,在数据中心存储和处理数据的爆炸性需求,以及传统的DDR内存接口的带宽和容量扩展有限的情况下,一些新型的接口互连技术被开发出来。

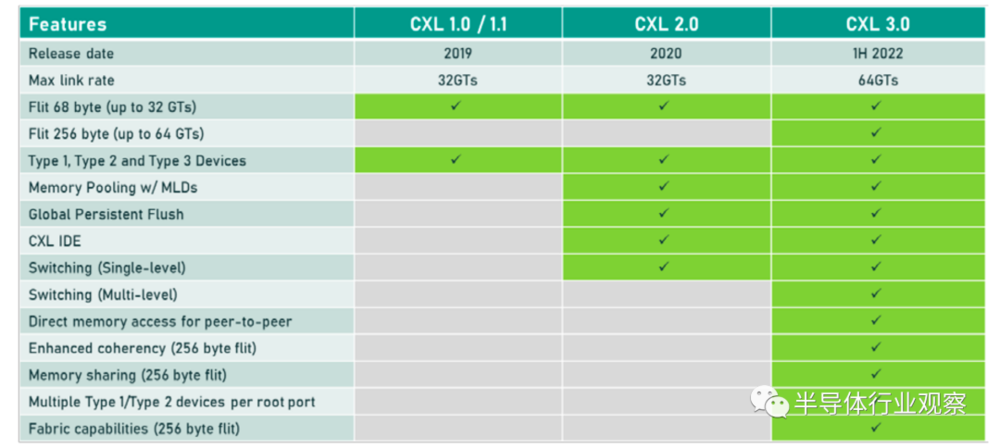

其中一个互连技术的挑战者是,英特尔于2019年3月在InterconnectDay 2019上推出开放性互连协议Compute Express Link (CXL) ,已成为业界和学术界认为最有前途的接口技术之一,因为它不仅可用于内存容量和带宽的扩展,还能够实现内存分解。这几年其标准发展迅速,不少芯片厂商已在其产品路线图中宣布支持CXL。

不同版本CXL对比(来源:CXL3.0白皮书)

另外一个就是现在大火的Chiplet,在后摩尔时代,Chiplet这样的先进封装技术在推动芯片性能继续提升上至关重要。其接口技术标准UCIe也于2022年推出,发展至今,UCIe联盟已经发布了两个版本,分别是UCIe 1.0和1.1。Chiplet当前正处于发展阶段,能否成为一种新的IP产品和商业模式,甚至拯救摩尔定律的救星,关键就在于业界能否达成统一的Chiplet互连标准,建立起来一个开放和标准化的Chiplet生态。

此外,还有一些公司推出独有的互连技术,例如英伟达的NVlink技术,它在今年早些时候推出了一款独立的128端口NVLink交换机系统,配备800G OSFP 接口,可直接连接多达256个Hopper H100 GPU。

硅光芯片也是一个有潜力的技术,随着近年来光子芯片赛道的厂商越来越多,例如英特尔、Ayar Labs、博通、思科、国内还有一大批企业如曦智科技等等。硅光子能提升光电传输的速度,有效解决目前计算机元件使用铜导线所遇到的信号耗损及热量问题,因此,被寄予厚望。但是硅光子还面临着高成本制造、光源集成、材料匹配、热效应等瓶颈。

据650 Group研究机构发布的《数据中心互连半导体预测与研究报告》中指出,数据中心计算现在和未来几年的发展代表着架构的转变。互连芯片的创新和技术转型将大幅提高每单位功率和每单位成本的系统I/O带宽,从而实现人工智能和加速计算集群的尺寸和代际的扩展。数据中心互连半导体市场(即支持跨计算、存储和网络系统的高性能数据通信的芯片技术的价值)预计将在2022年至2027年间翻一番,达到近250亿美元,年复合增长率达到两位数。

新的供电方式

随着我们不断缩小晶体管和 IC 的尺寸,供电成为一个重大的片上挑战。据应用材料的介绍,目前所有芯片都需要从芯片的前端提供电力,这大约需要通过超过12层的布线,直至晶体管。这种方法有两个主要限制:芯片上宝贵的空间必须分配给电源线,而且当电源穿过多层到达晶体管时会损失电源。背面供电(BPDN)或有助于拯救摩尔定律。

背面供电网络的基本思想是移除所有从硅表面上方发送电力(而不是数据信号)的互连,并将它们放置在硅表面下方。理论上这可以减少功率损耗,因为功率传输互连可以更大且电阻更小。它还为信号承载互连释放了晶体管层上方的空间,可能导致更紧凑的设计。

现在包括imec、英特尔(PowerVia)、台积电、三星等都在研发这项技术,一些芯片制造商已公开宣布在2nm及以上技术节点的逻辑IC中引入背面供电网络。但是背面供电技术需要创新的器件架构、新材料开发、材料的单片和异构集成、更大的晶圆尺寸和单晶圆处理,才能满足当今的应用要求。

新型材料

新型材料也是焦点之一。过去几十年,硅材料是芯片行业的统治者。根据宾夕法尼亚大学设备研究与工程实验室教授Deep Jariwala 的说法,“我们已经达到这样一个地步,即使你可以继续缩小硅,它已经到了不再节能的地步。”因此,行业研究学者对新型材料的探索孜孜不倦。潜在的硅替代者主要有二维材料如石墨烯、各种氧化物、金刚石、有机材料等等。它们被视为未来芯片技术的希望。

包括台积电和英特尔在内的商业企业,以及麻省理工、宾夕法尼亚大学等科研机构已经对二维材料进行了不同程度的研究,其中,大量的研究报告表明,基于二维过渡金属二硫族化合物如MoS2和WSe2的晶体管是接替硅的重要候选者。随着行业对二维材料研究的增加,其已经逐渐开始走向制造。

碳纳米管(CNT)是另一种被寄予厚望的新材料,被认为是下一代高性能、超大规模和薄膜晶体管以及光电器件的有力候选者。碳和硅一样,并不是什么新材料,从铅笔到钻石,碳无处不在。碳纳米管可能被用作高性能数字电子设备以及射频和传感应用的平台。而且它可以通过化学气相沉积(CVD)方法,能够在CMOS工厂成功制造。

二氧化铪这样的新型材料为存储乃至新型存储提供了更多的可能性。多项研究发现,二氧化铪具有铁电的特性,这样的好处是它能在不供电的情况下也可以长久存储数据,意味着其可以在非易失性内存领域发挥价值。

结语

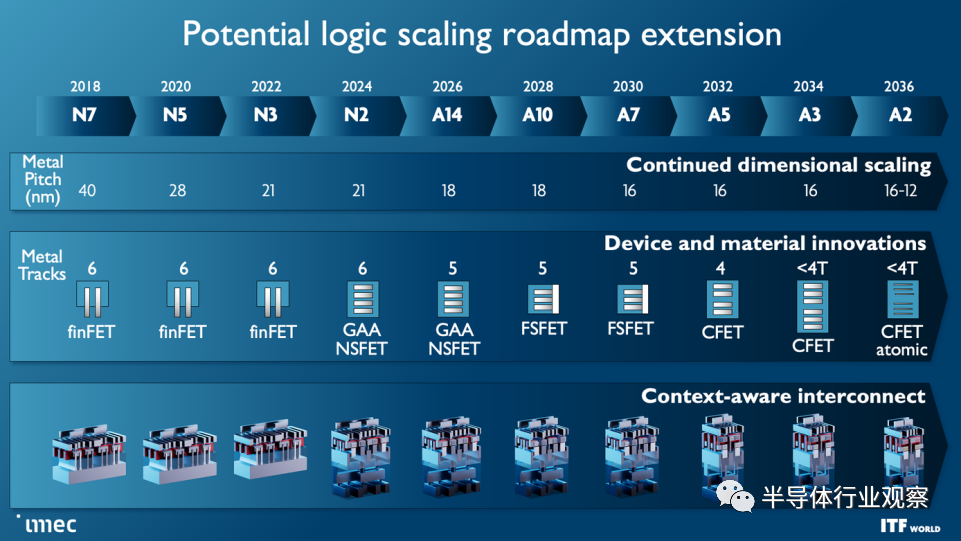

Imec预测,晶体管的形式将在未来十年发生变化,连接它们的金属也会发生变化。最终,晶体管可能是由二维半导体而不是硅制成的堆叠器件,电力传输和其他基础设施可以分层放置在晶体管下方。为了保持摩尔定律的正常运行,所有可能的杠杆都将被拉动,除了上文所提到的这些,还有下一代光刻技术、工具等各领域的支持。最终,我们能将摩尔定律延伸到什么程度很可能是一个纯粹的经济学问题。

Imec的CMOS 2.0路线图,很有趣

本文来自微信公众号:半导体行业观察 (ID:icbank),作者:杜芹DQ