扫码打开虎嗅APP

本文来自微信公众号:半导体行业观察 (ID:icbank),作者:编辑部,头图来自:视觉中国

昨天,有一个新闻在半导体圈广为传播,那就是全球首台High-NA EUV光刻机正式发货。在行业看来,这个售价高达四亿美元的设备,是未来制造2nm以下芯片的关键。除了光刻机以外,忽然还需要更多的新设备、新材料和新工具来实现2nm。因此,这个节点的成本大涨,是可以预见的。

International Business Strategies的分析师在接受日经采访的时候更是直言,2nm带来的成本会更恐怖,与3nm处理器相比,增长约50%,这就意味着届时2nm芯片每片晶圆的价格将达到3万美元。

正如tomshardware所说,IBS 的每芯片成本估算实在引人注目。

一、设计成本,7.25亿美元

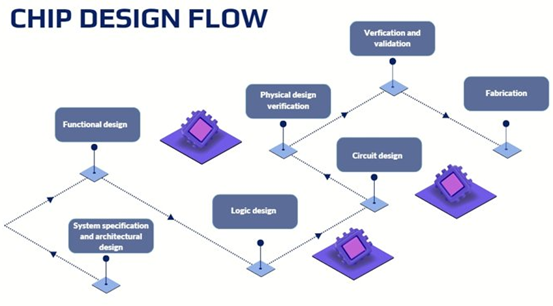

首先,我们从设计端来讨论一下2nm芯片的成本。在具体谈成本之前,我们先说一下设计一个芯片的流程。

资料显示,芯片设计流程的第一步是定义芯片的要求和规格。这包括定义您的产品将做什么、如何使用以及需要满足哪些性能指标。一旦定义了这些要求,它们就可以用作设计架构和布局的输入。

确定要求后,芯片设计的下一步是创建满足这些要求的架构,同时考虑将成本和功耗降至最低等因素。在芯片设计的初始阶段,设计人员对架构做出关键决策,例如在RISC(精简指令集计算机)或CISC(复杂指令集计算机)之间进行选择、确定所需的ALU(算术逻辑单元)数量、决定管道的结构和数量、选择缓存大小以及其他因素。

因为这些选择构成了设计过程其余部分的基础,因此设计人员仔细评估每个方面并考虑它将如何影响芯片的整体效率和性能至关重要。这些决策基于芯片的预期用途和定义的要求,最终目标是创建高效且有效的设计,同时最大限度地降低功耗和成本。

完成架构设计阶段后,设计人员创建微架构规范 (MAS:Micro-Architectural Specification),这是芯片架构的书面描述。该规范使设计人员能够准确预测设计的性能、功耗和芯片尺寸。通过创建全面的MAS,设计人员可以确保芯片满足初始设计阶段建立的要求和规范。彻底的MAS对于避免流程后期出现错误并确保芯片设计符合所需的性能标准和时间表至关重要。这可能涉及在不同的处理器类型或FPGA(现场可编程门阵列)之间进行选择。

之后,我们还要进行以下步骤:

功能设计

该过程涉及定义芯片的功能和行为。这包括创建系统需求的高级描述以及设计满足这些需求所需的算法和数据流。此阶段的目标是创建一个功能规范,可用作其余设计过程的蓝图。

逻辑设计

此步骤涉及创建实现功能设计阶段定义的功能所需的数字逻辑电路。此阶段包括使用硬件描述语言 (HDL)创建逻辑设计并使用仿真验证设计的正确性。

电路设计

此阶段涉及设计芯片的物理电路,包括晶体管、电阻器、电容器和其他组件的选择。电路设计阶段还涉及芯片的电源和时钟分配网络的设计。

物理设计验证

物理设计验证是检查芯片物理布局的过程。这涉及识别任何设计问题并确保芯片能够正确制造。在此步骤中,通过逻辑模拟器、逻辑分析仪等EDA软件工具以及设计规则检查(DRC)、布局与原理图(LVS)以及时序和功耗分析等各种技术来验证集成电路布局的设计,以确保正确的电气和逻辑功能以及可制造性。

验证和确认

完成芯片设计后,就可以对其进行测试了。这称为验证和确认 (V&V:verification and validation )。V&V涉及使用各种仿真和模拟平台测试芯片,以确保其满足所有要求并正确运行。如果设计中有任何错误,它会在这个开发阶段显现出来。验证还有助于确定少数最初制造的原型的功能正确性。

最后则是物理布局设计的制作。在芯片设计和验证后,GDS文件被发送到代工厂进行制造。

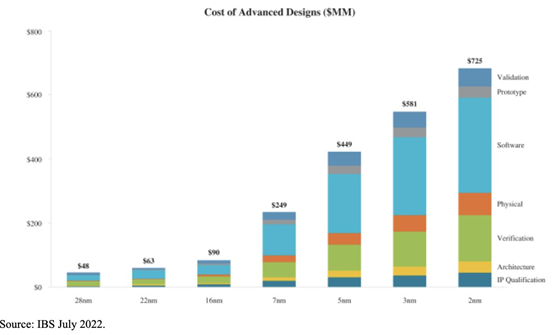

正因为拥有如此多步骤,可以预见芯片设计过程中需要涉及多少的工具和软件之前,IBS有一张图广为流行。如下图所示,它展示了不同节点下生产一颗新芯片的成本。从这个图中我们可以看到,芯片设计成本不但包括了各种IP的授权费用,还包括了软件和验证带来的支出。如图所示,在5nm的时候,芯片的设计成本已经高达5.4亿美元。

而在进入到了2nm之后,这个数据更是进一步飙升。

根据IBS的一份芯片设计成本预估,设计一颗2nm 芯片的开发总计将达到7.25亿美元。如图所示,在芯片设计的成本中,软件占据了大头,其次是Verification、Validation、物理、IP授权、原型和架构。这是可以理解的,因为先进技术给芯片设计行业带来了巨大挑战,所以软件开发和验证占芯片设计开发成本的最大份额。例如在2nm,软件成本就高达3.14亿美元,验证成本也达到了1.54亿美元。

值得一提的是,原本在28nm的时候,软件是芯片设计的最大成本,但这种情况在22nm和16nm时发生了逆转。然而进入10nm后,这种情况又出现了。

二、晶圆厂,280亿美元

关于晶圆厂的成本,我们看到了很多详细的介绍,但其实并没有太多详实的参数介绍。因为在不同的工艺、不同的产能情况下,使用到的设备、工具和材料成本也不太一样。和介绍设计成本一样,我们先要介绍一下晶圆厂的成本构成:分别是建设晶圆厂的成本和产线上设备的成本。

首先看建厂方面,一般而言,晶圆厂的建筑负责保护芯片产线免受周围环境的影响。晶圆厂的核心是洁净室,里面装有生产新芯片的机器。晶圆厂的其余部分负责尽可能地将洁净室与外界环境隔离。下图提供了铸造厂的横截面图。请注意,因为我们需要大量的结构隔离工作来稳定包含洁净室的生产水平,所以这部分的建设工作最终可能成为整个主体结构中最昂贵的部分。

同时,晶圆厂还需要在换气、空气净化等方面做一个投资,虽然比较复杂,但是建设成本通常仅占半导体代工厂总成本的10~20%左右。绝大多数成本(约 70~80%)由晶圆厂内的实际设备占用。

根据SEMI在2017年公布的数据,在集成电路制程中,晶圆制造设备投入占比约占设备投资的80%,而封装、测试设备投入则占比分别为9%和6%。在制造过程中,最主要、价值最昂贵的三类分别是沉积设备(包括PECVD、LPCVD等)、刻蚀设备、光刻机,他们占半导体晶圆厂设备总投资的15%、15%、20~25%。

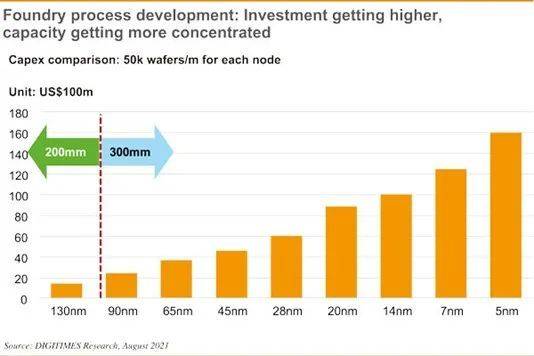

如文章开头所示,随着节点的缩小,光刻机的成本水涨船高,整个晶圆厂的成本大幅提升也是理所当然的。

根据Digitimes在一篇文章中预估,如下图所示,一座每月可生产50000片90纳米晶圆的12英寸晶圆厂耗资约为24亿美元。一旦推进到28纳米,同等规格晶圆厂的成本将达到60亿美元,5纳米晶圆厂的成本更是高达160亿美元。

来到3nm晶圆厂,台积电创办人张忠谋在2017年接受彭博社采访的时候曾透露,建设一个3nm晶圆厂的成本将会高达200亿美元。由此可以看到光是花在制造晶圆厂上的价钱就十分惊人。

而从IBS提供的数据可以看到,每个工艺节点的投资成本和上述Digitimes所提供的数据是详尽的。在进入到2nm之后,据IBS透露,光是晶圆厂成本就高达270亿美元,这无疑给厂商设定了一个极高的门槛。

同时,正因为拥有如此高的晶圆厂成本,叠加工具的涨价,就会让2nm芯片的成本显而易见。

以苹果的芯片为例,据IBS预计,苹果目前的3纳米芯片成本约为50美元,但并未定义芯片尺寸。Arete Research估计,苹果最新的智能手机A17 Pro片上系统的芯片尺寸在100mm2至110mm2之间,与该公司上一代 A15 ( 107.7mm^2 ) 和 A16的芯片尺寸一致(比 A15 大约 5%)。如果苹果 A17 Pro 的芯片尺寸为105mm2,那么一块300mm晶圆可容纳586个芯片,这使得其成本在假设的100%良率下约为34美元,在更现实的85%良率下成本约为40美元。

International Business Strategies 进一步估计,使用2nm工艺的“苹果芯片”成本将从50美元上涨到85美元左右,这意味着良率相当低。按每片晶圆30000美元和85%的良率计算,单个105mm2芯片的成本为60美元。当然,这是一个非常粗略的估计。

相比之下,今年早些时候的预测表明,台积电晶圆厂每片2nm晶圆的成本为25000美元,这提醒我们,估算可能会有很大差异。

即使对2nm晶圆厂成本和晶圆成本进行非常粗略的估计,很明显,使用2nm节点制造的芯片将比使用3nm级工艺技术生产的处理器更昂贵。也就是说,预计AMD和英特尔等公司将在未来几年加速采用由不同节点上制造的小芯片组成的多芯片组设计,从而支付与领先节点相关的成本。与此同时,由于先进封装成本仍然相当高,那就意味着智能手机处理器可能会在一段时间内保留单片设计。

成本越来越高,未来还有多少公司会继续追求先进芯片?未来谁能承担起这样高昂的成本,不禁成为了我们思考的头等问题。

参考链接

https://www.tomshardware.com/tech-industry/firm-predicts-it-will-cost-dollar28-billion-to-build-a-2nm-fab-and-dollar30000-per-wafer-a-50-percent-increase-in-chipmaking-costs-as-complexity-rises

https://www.design-reuse.com/articles/54033/an-outline-of-the-semiconductor-chip-design-flow.html

https://deepforest.substack.com/p/a-deeper-dive-into-semiconductor

本文来自微信公众号:半导体行业观察 (ID:icbank),作者:编辑部