扫码打开虎嗅APP

本文来自微信公众号:TechSugar(ID:TechSugar),作者:郭紫文,题图来自:视觉中国

超越台积电,是三星一直以来的梦想。早在2017年三星晶圆论坛上,其相关负责人便扬言,三星要超越联电和格芯,晋升为全球晶圆代工第二名,未来还要挤掉台积电,成为代工市场龙头。超越联电和格芯的目标于2018年便已实现,而与台积电的差距却始终难以跨越。

在工艺制程不断演进的过程中,越来越多的参与者被淘汰出局,如今先进制程玩家仅剩下台积电、三星和英特尔三家公司。为了追赶台积电,三星在先进制程的布局上略显激进。在资本支出方面,2021三星芯片业务资本支出超360亿美元,超越同年度台积电的投资规模。而在先进工艺研发方面,三星也欲抢先台积电,实现3nm芯片量产,并率先采用GAA工艺。

然而,三星的巨额投资似乎并未取得预想成效。前段时间,三星晶圆代工被曝出“良率造假”,正深入调查资金流向及产量报告等问题,重点关注5nm至3nm良率。造没造假不得而知,但三星深陷良率泥潭久矣,4nm良率仅为35%,反观台积电4nm制程工艺芯片的良率可达到70%,是三星的两倍。正因为良率问题,三星晶圆代工的主要客户正在流失。高通决定将骁龙8 Gen1订单转向台积电生产,后续3nm芯片也全量委托给台积电;英伟达RTX 40系列显卡也将采用台积电5nm制程。

在此境况下,三星离晶圆代工第一把交椅渐行渐远。为了挽回局面,三星近期也是动作频频。据韩媒报道,三星电子日前调整了其组织架构,设立测试与封装中心,企图扩大封测领域投资布局力度。另外,在先进制程上的失利,让三星开始考虑提高其成熟工艺产能,以进一步优化产能与成本,提高芯片代工营收,增强市场竞争力。

相较于台积电,2005年才踏入晶圆代工业务的三星无疑是后进者。此后十余年内,三星晶圆代工业务一路披荆斩棘,超越了格芯、联电等前排厂商,逐渐比肩台积电。事实上,据IC Insights数据显示,截至2009年之前,三星晶圆代工业务营收尚未超出4亿美元,市场占有率很低。

进入2011年,三星的研发实力逐渐开始突显。在28nm成熟制程,三星于2012年实现量产,并于次年导入了28nm HKMG工艺。在此方面,台积电仅比三星领先一年,而联电与格芯28nm制程于2013年才开始量产。

随后,工艺制程演进至14nm及以下先进节点,联电宣布退出14nm FinFET以下先进制程技术研发,格芯也放弃了12nm以下先进制程技术投入。在晶圆代工市场上,仅剩下台积电、英特尔、三星以及中芯国际等厂商还在推进先进制程的演进。自2017年晶圆代工业务独立以后,三星与台积电在先进制程上的竞争也越来越焦灼。从量产时间来看,在7nm及以下工艺制程,三星与台积电你追我赶,不分伯仲。

图:三星先进制程演进

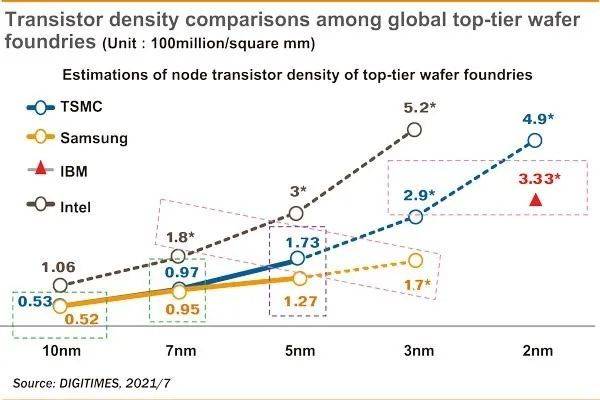

然而从DigiTimes数据可以看出,各个厂商对工艺制程的定义并没有统一的标准,单从晶体管密度看,三星3nm工艺制程还不如英特尔7nm(已改为Intel 4)。三星3nm工艺制程晶体管密度达1.7亿颗/平方毫米,而台积电5nm工艺制程晶体管密度达1.73亿颗/平方毫米,英特尔7nm工艺制程晶体管密度达1.8亿颗/平方毫米。但晶体管密度仅作为衡量半导体工艺水平的一个参考,具体到应用中,还需要从材料、功耗、性能表现、成本、良率等多方面进行考量。

对于半导体制造,良率直接关乎着芯片量产成本,对产品品质和可靠性也有一定影响,同时也牵涉着客户信任度和满意度。良率越高,每片晶圆上质量合格芯片数量就越多,每颗芯片的成本就越低。因此,对三星而言,晶体管密度追不上台积电并不是重点,关键是如何解决良率问题。

相比之下,三星4nm制程良率约35%,而台积电同制程良率则为70%,这意味着三星的晶圆代工成本将高于台积电两倍不止。而良率造成的成本上升,直接劝退了高通、英伟达在内的主要客户。

在先进制程争夺战中,良率是一个很关键的因素。而工艺制程越是先进,工艺难度越高,良率越是难以保障。影响良率的因素多种多样,从晶圆制造到封装测试,半导体制造每个流程都有可能造成芯片良率损失。显然,单在良率方面,三星便落了台积电一大截。若想超越台积电,三星首先要解决的便是先进制程的良率问题。

在追赶台积电的过程中,三星因良率问题遭到了客户信任危机。然而,其对先进制程的激进策略并没有止步。在3nm工艺制程上,台积电仍基于FinFET工艺,而三星则率先转向了GAA晶体管工艺。三星表示,该公司将按照时程在2022年下半年领先全球推出商用GAA芯片工艺。据报道,三星拟于2022年上半年完成3nm GAA工艺质量评估,并计划于今年6、7月份在韩国平泽市P3工厂开工建设3nm晶圆厂。

作为FinFET的继任者,GAA(全环绕栅极)晶体管在性能、功耗、静电特性方面都有着显著提升。同等尺寸结构下,GAA的沟道控制能力比FinFET更强,为尺寸进一步微缩提供了可能性。三星也表示,与7nm工艺制程相比,3nm GAA工艺逻辑面积效率提高45%,功耗降低50%,性能提高了35%。

然而,理论参数性能的提升并不意味着可以满足客户在性能产能及良率方面的需求。韩国远大证券显示,截至2020年,三星晶圆代工IP不超过1万项,而台积电IP数则已经达到3.5万至3.7万项。在3nm GAA工艺相关IP方面,三星相对落后于台积电。这也让业界对三星在3nm GAA工艺中的良率及性能表现充满了质疑。

整体而言,客户流失、IP匮乏等问题都将使三星的工艺演进面临巨大挑战。要知道,在晶圆代工领域,资本投入、技术和经验将形成正向循环,代工厂以巨额投资驱动技术迭代,从而换取客户资源,而后通过客户量产经验提升良率,从而反哺企业进行下一代技术研发。这就不难理解晶圆代工领域为何会形成寡头垄断格局了。

在先进制程继续发力的同时,三星也在转变思路,考虑提高成熟工艺制程的产能,不断优化和改进旧制程,提高产品性能和成本竞争力。去年10月,三星对17nm FinFET工艺制程技术进行了升级优化,并将其应用于原本28nm制程生产的影感测器和行动显示驱动芯片(DDI)的生产中,进一步提高了生产效率。

除此之外,三星还与英特尔、台积电等企业参与成立了Chiplet标准联盟UCIe,并设立测试与封装中心,加码先进封测领域技术投资。随着摩尔定律式微,新材料、新工艺、新架构逐渐成为延续摩尔定律的关键,异构集成与先进封装也将成为未来发展的主流趋势。可以看到,晶圆代工领域的头部厂商们都将先进封装及测试作为一大战略方向。

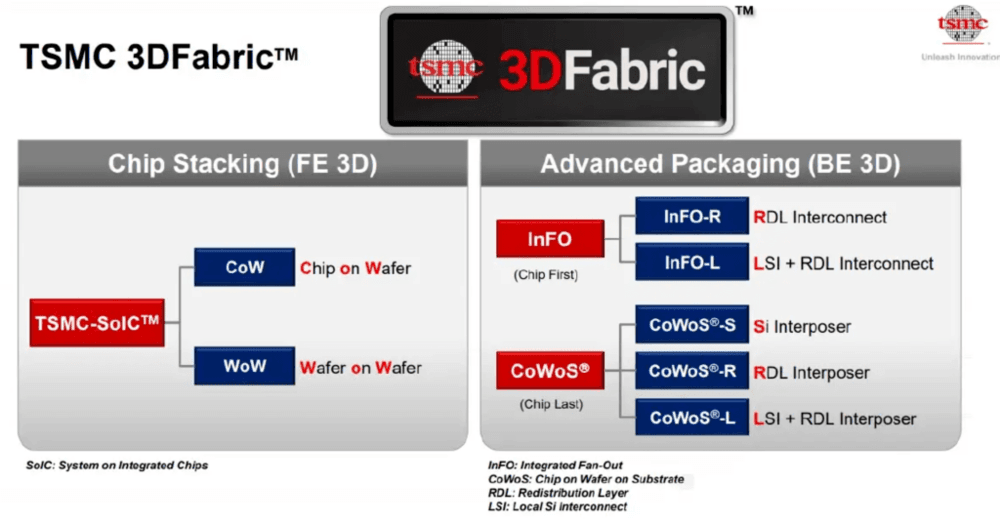

台积电在先进封装领域布局已久,2020年,台积电推出了3DFabric技术平台,该技术平台包含台积电前端芯片堆叠SoIC技术和后端先进封装CoWoS和InFO技术。

相对而言,三星在先进封装领域的技术实力较为薄弱。2020年,三星宣布其3D封装技术X-Cube;去年11月,三星又推出了全新2.5D封装解决方案H-Cube(混合基板封装)。为在后摩尔时代继续提高芯片性能,三星未来将加大先进封装投资力度,提高先进封装技术研发实力。

据TrendForce集邦咨询数据,2021年第四季度,台积电营收达157.5亿美元,市占率52.1%,三星则为55.4亿美元,市占率18.3%,有着不小的差距。随着今年资本支出不断飙升(台积电2022年资本支出预计提升至400至440亿美元;三星预计2022年资本支出320亿美元),预计晶圆代工市场竞争将更加激烈。

另一方面,在2nm工艺节点上,台积电也将转向GAA工艺,而英特尔则计划在Intel 20A工艺改用GAA晶体管(英特尔称RibbonFET晶体管)。现阶段,英特尔宣布开放代工服务,并收购了高塔半导体。届时,在2nm工艺制程争夺战中,三星将与台积电、英特尔正面“厮杀”。

本文来自微信公众号:TechSugar(ID:TechSugar),作者:郭紫文