扫码打开虎嗅APP

本文来自微信公众号:差评 (ID:chaping321),撰文:小陈,编辑:面线,题图来自:视觉中国

上个月啊,华为开了自家的年度财报大会,向大家公布了自己去年一年的营收结果。

营收 6368 亿,同比下降 28.6%。利润 1137 亿,同比增长 75.8%。看起来在好像是华为在被制裁后还给出了一份不错的答卷,但是另一方面,我们也都知道它失去了什么。

所以在发布会上,被问到和芯片相关的问题时,华为的轮值董事郭平说了这么一句话:

“解决芯片问题是一个复杂的漫长过程需要有耐心,未来我们的芯片方案可能采用多核结构,以提升芯片性能。”

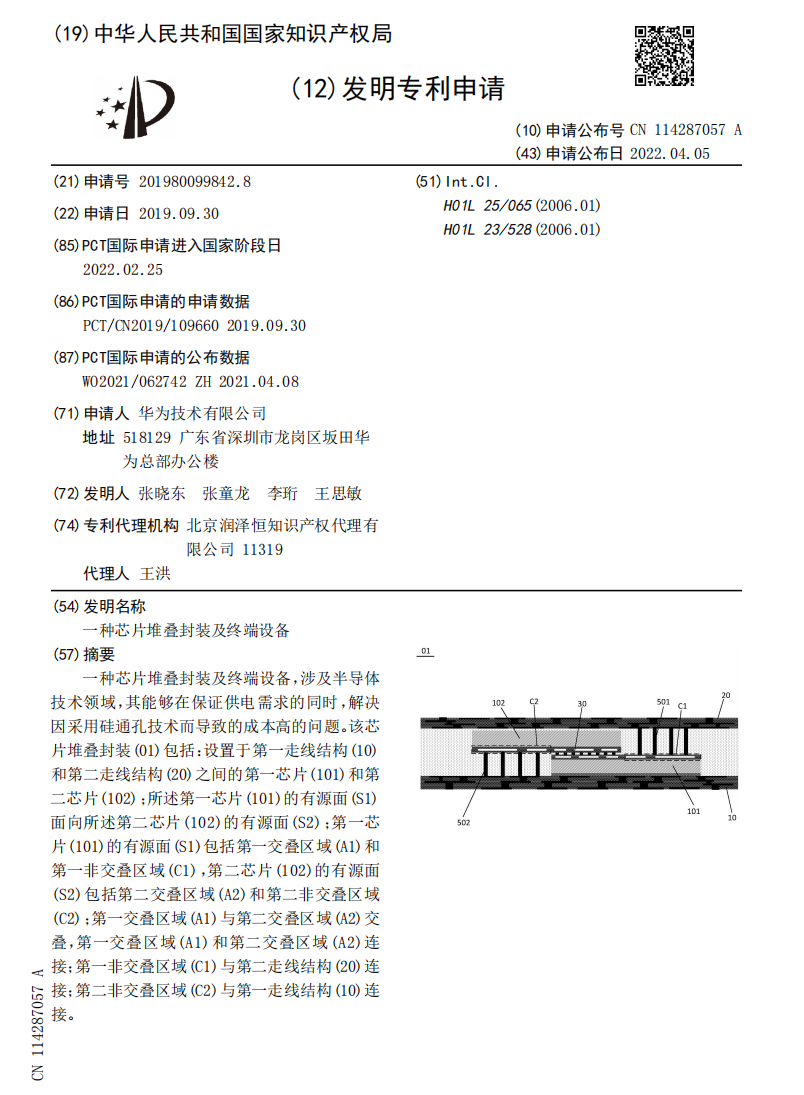

然后没过几天,华为就公布了一项“芯片堆叠”的专利。去年的小道消息,居然……

虽然这次公布的专利只有一页,但是关于华为是否能够使用“双芯叠加”的技术的讨论,总算是进入到了第二个阶段。

所以,现在也是时候重新来盘一盘这项名叫芯片叠加——或者说“先进封装”的技术了。

它是个新鲜概念吗?它又真能实现 14 nm 工艺造出 7 nm 芯片的效果吗?大家别着急,咱们一步一步慢慢聊。

芯片叠加,新鲜概念?

其实不是,英特尔在二十年前奔腾 D 的时代就搞过类似的技术了:

当年还和 AMD 在这方面吵了一波口水架。

以及,这几年咱们身边不少的芯片:比如 AMD 的线程撕裂者,Intel 的 12 代酷睿,苹果的 M1 Ultra。它们多多少少也有用上先进封装工艺,也算是叠加芯片。

所以华为说要搞“双芯叠加”,从芯片制造工艺的角度讲,是靠谱的。

M1 Ultra 发布的演示图

不过话说到这里,可能大家还是对芯片叠加(先进封装)的概念一头雾水。

所以要想继续往下说,我们得先介绍一下先进封装的好兄弟——先进制程。所谓先进制程,其实就是指的每年最新的芯片制造工艺:前年是 7nm,去年是 5nm。到了明年估计该到 3 nm 了。

但是吧,这晶体管的体积也不能无限制的缩小。而且单颗芯片的面积大小又有一定的限制,不能无限制的弄大。

所以,像苹果 M1 Ultra、AMD 5800X3D 这类把好几颗小芯片连成一个整体的“多芯融合”设计,被大家给整了出来。

同时,先进封装的概念也被摆到了台面上。所谓先进封装,其实就是用来“提高多个芯片之间的互访和沟通能力”的技术。

大家别急,下面我用人话把这句话解释一遍。

不少小伙伴可能对前些年的显卡交火还有点印象,在老黄那儿叫 SLI,能让两张显卡同步处理工作。听起来和这个“双芯叠加”是不是有些像?

当年这技术出来的时候是讲的天花乱坠啊,比如说什么可以同步渲染啊,画质增加啊,能够交替渲染,显著提升游戏帧率啊……

可结果大家兴冲冲的拿过来一尝试,结果发现提升最大的场景是在用鲁大师跑分。帧率不稳定,还有画面撕裂的问题……这别说提升了,能不拖后腿就算好了。

这问题其实出在芯片间的互联能力上:电路板的两端就好像是隔着十万大山,两颗芯片间的信息交换严重受阻。所以任务无法分配,交叉验证过程受阻,协同计算更是无从谈起。

换句话说,以前的双核芯片就好比是雇了两个互不联系的秘书——谁都以为对方在干活,所以最后没人在干活。效率反而没只有一个核心来的高。

而先进封装呢,其实就是把两颗芯片之间的大山凿穿,用数不清的电路把两颗芯片间的互访安排了个明明白白。每颗核心的任务也就安排了个明明白白。

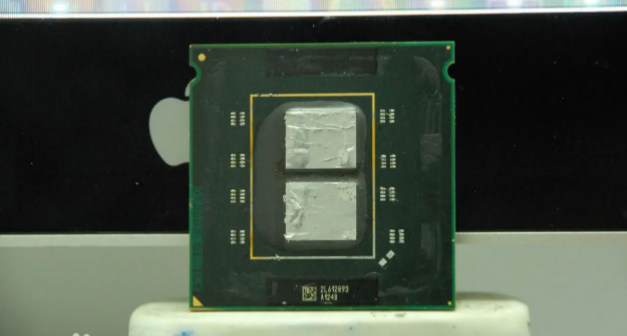

前一阵苹果大火的 M1 Ultra 就用上了来自台积电的先进封装工艺,结果大家也看见了:两颗独立的 M1 Max 芯片粘在一起,非但没有像以前的双核芯片那样性能极度拉跨,反而几乎实现了 1+1 = 2 的性能提升。

可以说,先进封装是在先进工艺受阻的情况下,通过“多芯融合”实现性能提升的先决条件。

这么神奇的东西是怎么做到的呢?

过去的芯片和芯片之间想要互相沟通,需要把它们插到电路板上才行。而先进封装就不一样了,不需要绕这么多花花肠子。

别看目前的先进封装工艺有三星的 FOSiP I/X/R/H-Cube,台积电的整合 3DFabric,其中包括InFo-PoP/oS,InFo_SoW,CoWoS-S,SoIC。英特尔的 EMIB,Foveros,Foveros Omni/Direct,还有英飞凌的 Fan-out 等等等等。

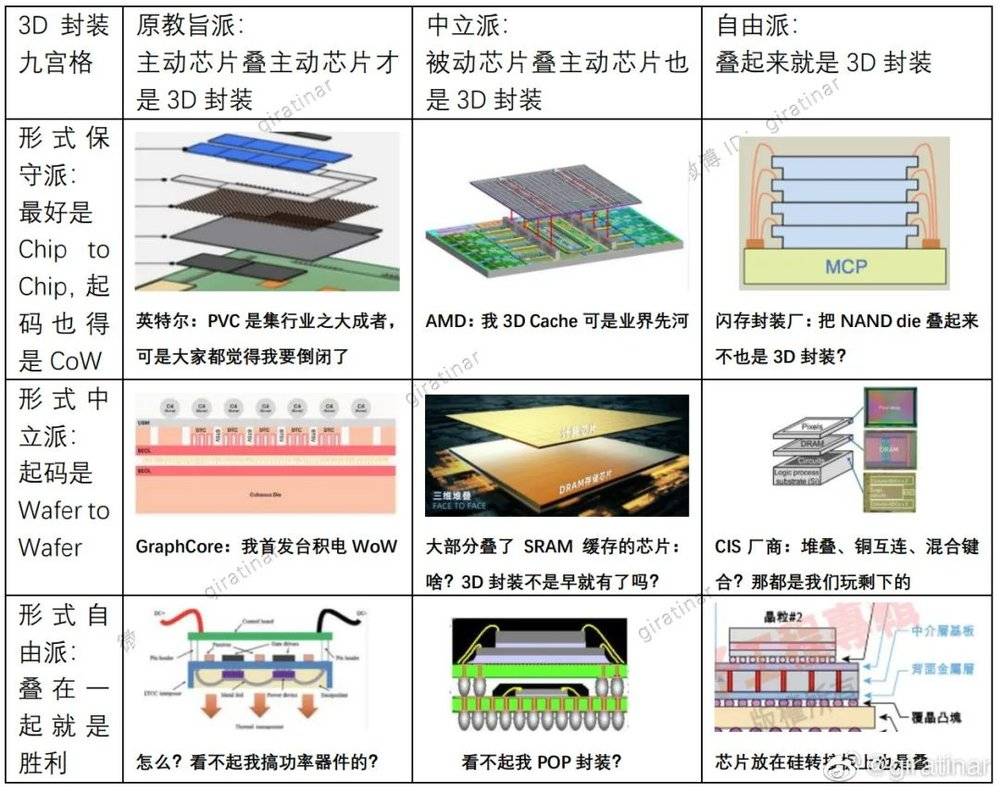

图源:weibo @giratinar

但其实它们的目的都是一样的:就是让芯片们面对面贴贴!

这样的好处毋庸置疑,芯片贴贴互联,信号之间传输的路径更短,通讯频率更高,芯片总体积更小,不用再像以前那样,走又慢又堵的 PCB 板才能通讯了。

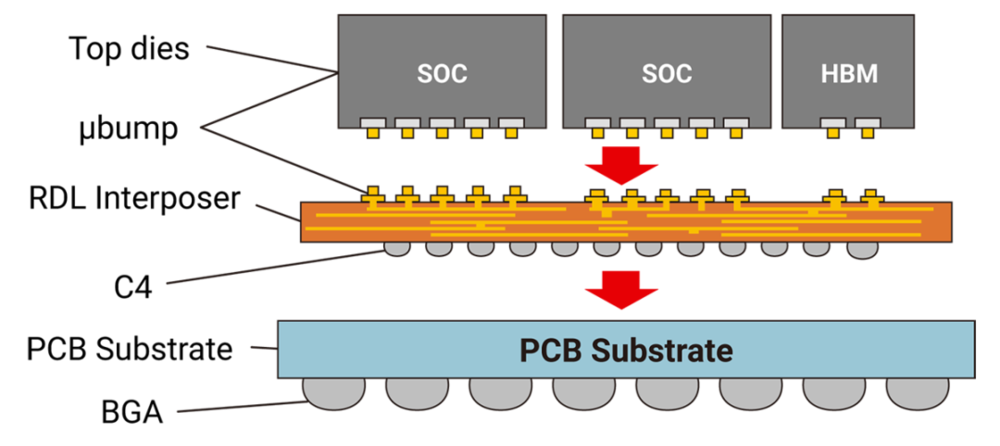

这里就拿台积电的 CoWoS-R 来举个例子。

其中的 CoWoS 是基板 叠晶圆 再叠芯片( Chip-on-Wafer-on-Substrate )的意思,后面的 R 是指图中的有机基板中间层(RDL Interposer)。

在这个封装中,相当于在芯片底下的有机基板中间层里凿穿了一大条地铁网络,让跨芯片的数据沟通变得非常的顺畅。

只要这 “地铁网络” 修的到位,就相当于就是在原有制程不变、单芯片大小不变的情况下,翻倍了晶体管的数量,也实现了最终目标——获得更出色的芯片性能。

欸不过吧,话又说回来了。咱们都知道芯片生产是一个牵一发而动全身,高度耦合的行业,这先进封装看起来好处多多,可又有哪些代价呢?

“先进”带来了什么?

首先,新工艺嘛,对生产和研发他们的工厂来说,自然是又贵又难。

而且吧,先进封装生产出来的双核心处理器并不一定适合所有形态的电子设备。因为虽然先进封装解决了两颗芯片同时运行性能拉跨的问题,做到了 1+1 ≈ 2。

但是先进封装多颗芯片却是彻底反着来的:我不是用更先进的工艺换性能,而是用更大的芯片规格换性能。在性能(不一定能)翻倍的同时,两颗芯片产生的功耗和发热,却可能是 1+1 > 2。

又大又热又费电,这就和手机厂商们的目标有些背道而驰了。所以以往多芯封装的产品大多见于台式机、服务器这种不需要考虑续航的设备;苹果的 M1 Ultra 也是给了插电的 Mac Studio,而非用电池的 MacBook。

假如说,华为真的要采用双芯叠加的先进封装,那么大概率首批采用的设备也是鲲鹏系列台式机,而不是麒麟手机处理器。不然那个发热和续航不见得会很好看。

不过,虽然我觉得华为的手机不见得会上双芯封装的处理器,可是大家别忘了,先进封装工艺的范围可不仅限于把两颗 CPU 粘在一起。还可以给 CPU 贴贴上一些“有意思”的东西。

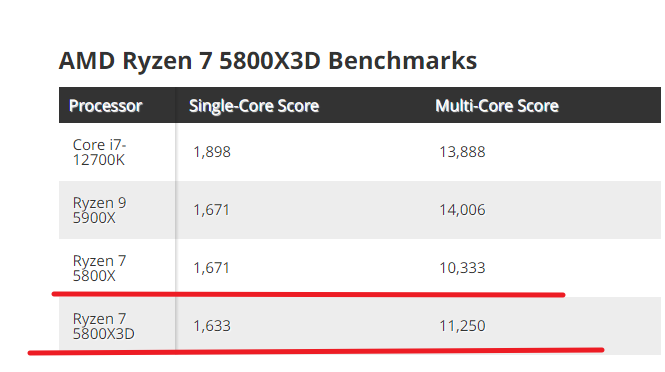

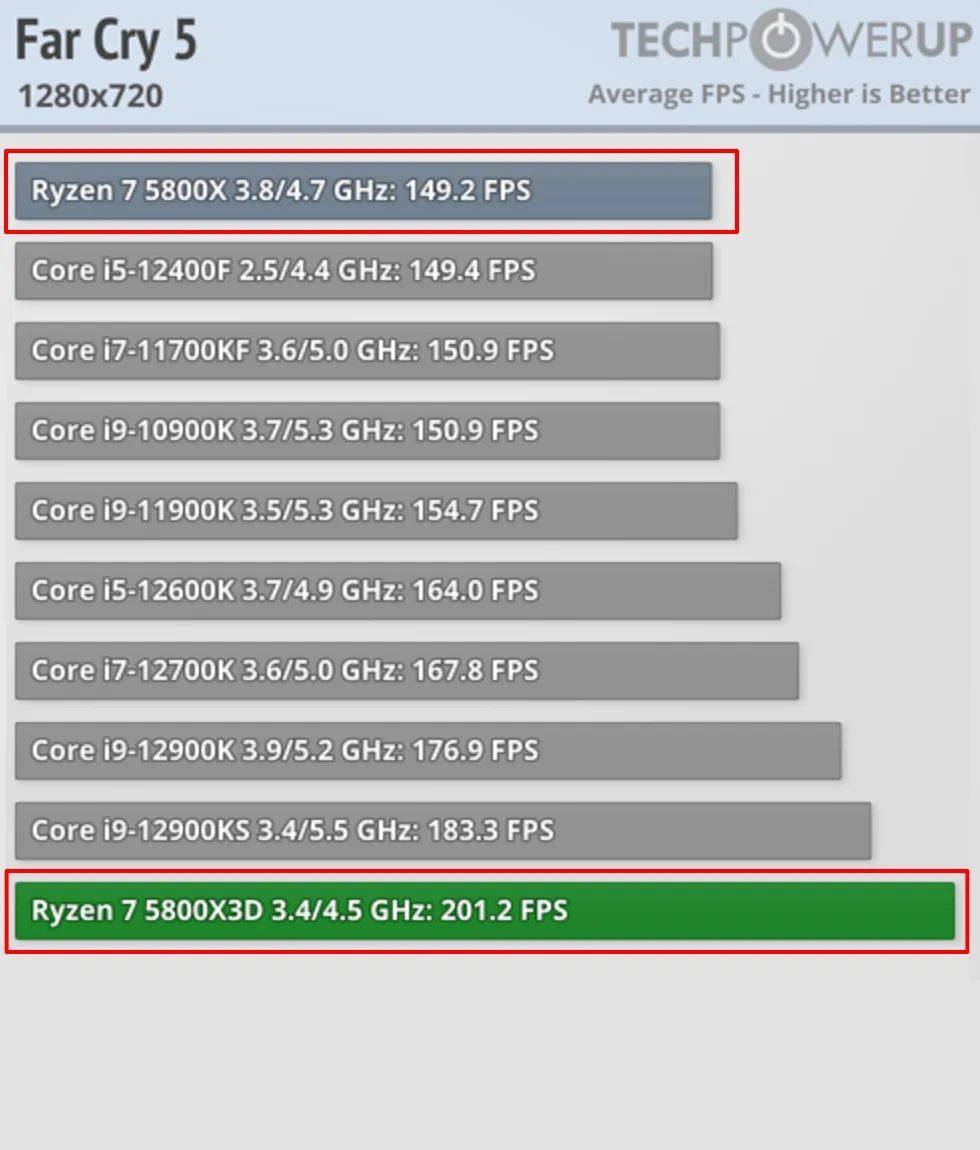

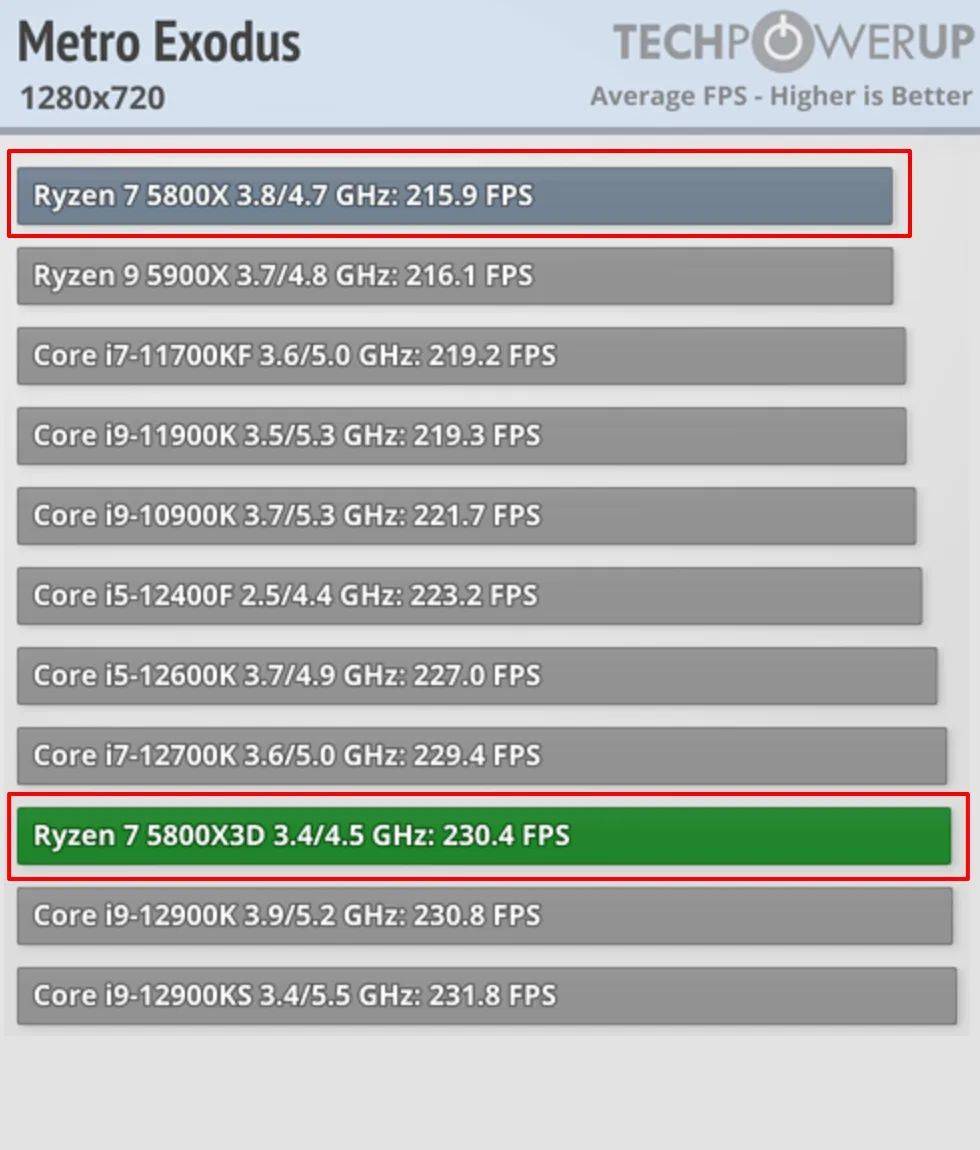

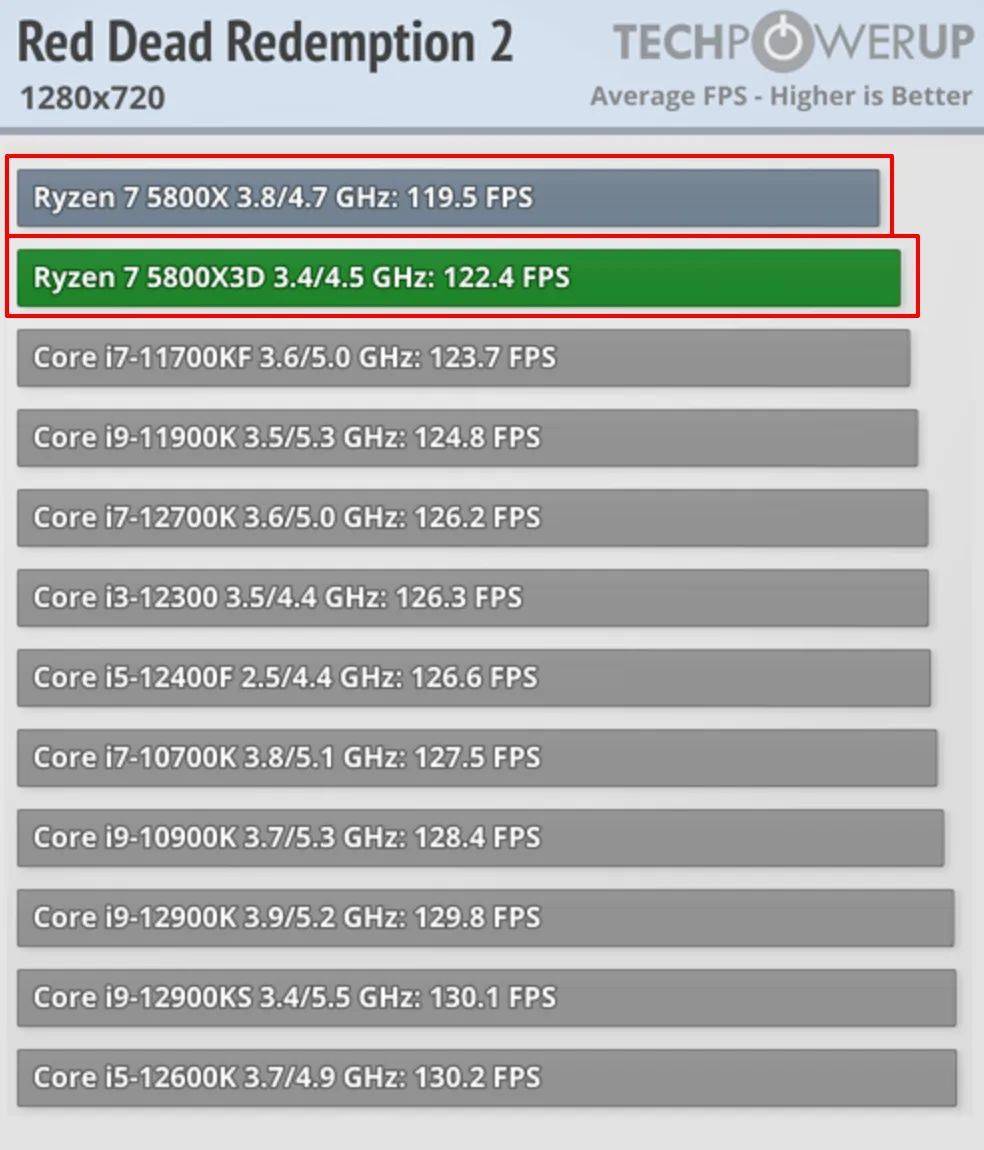

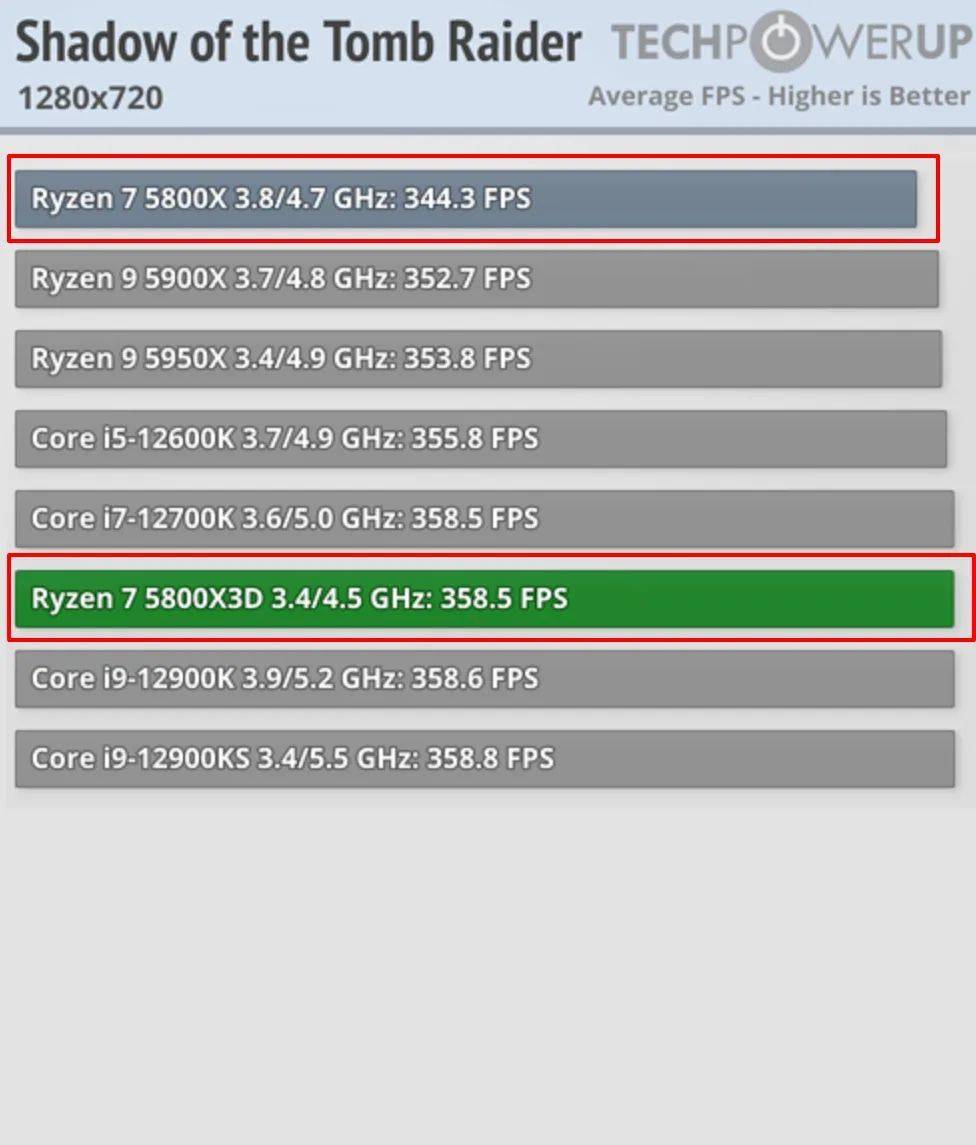

就比方说——AMD 即将发布的 5800X3D 先进封装处理器,里面的 CPU 核心还是只有一颗,真实性能跑分没比以前的 5800X 强多少。

比隔壁的英特尔 i7 都差了一大截。

但是它打游戏的帧数暴涨,能跟理论性能强了一圈的 i9 打的有来有回。

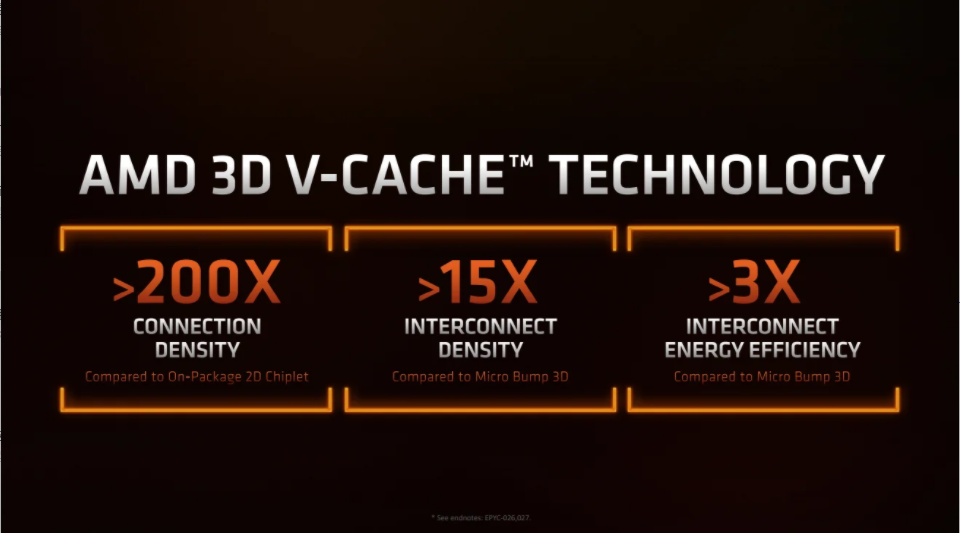

就是因为 AMD 通过先进封装工艺,把 CPU 内核和缓存芯片贴在了一起。CPU 到闪存的连接密度是传统封装工艺的 200 倍。

反映到实际场景中,就是降低了游戏掉帧和卡顿的概率——因为 CPU 读取指令和输出结果的环节变得更顺畅了。

这种先进封装的路线,说不定才是华为真正想采用的。

不过话又说回来了,虽然先进封装是一项解决制程工艺精度不足的好技术。假如华为用好了,14 nm 的芯片打 7 nm,7 nm 的打 5 nm 并非是一句空气。

可是,费力折腾先进封装的前提是“工艺受限”,这是一切问题的根源。

所以要我说,我不想看华为拿 14 nm 的芯片打别家 7 nm 的芯片。我希望看到的场景,还是华为能像友商们一样,用上半导体行业最新的工艺和技术。作为一个“芯片搅局者”,再造出一款像麒麟 9000 这样的神 U。

图片、资料来源:

华为2021 年报 https://www.huawei.com/cn/annual-report

http://www.icfgblog.com/index.php/process/158.html

先进高性能计算芯片中的扇出式封装(上篇)

制程工艺演进之路最终会走向何方?——尖端工艺背后的资本与科技角力

中金 | 半导体制造系列:先进封装扮演更重要角色

解读先进封装:全球11家大厂的选择

后摩尔时代,先进封装将迎来高光时刻 | 马盛林

AMD Ryzen 7 5800X3D Review - The Magic of 3D V-Cache

本文来自微信公众号:差评 (ID:chaping321),撰文:小陈,编辑:面线