扫码打开虎嗅APP

本文来自微信公众号:科工力量 (ID:guanchacaijing),作者:铁头哥,头图来自:视觉中国

聊完猴子后,铁头一直在关注芯片行业。一方面,是三星会长李在镕去了一趟ASML,谈的能是采购光刻机的事。另一方面,台积电最近举办了北美技术论坛,公布了不少新工艺。

这两家大厂反应这么大,主要是为了布局未来的2nm制程。如果说以前的90nm,28nm,14nm属于“性能极大改善”的话。3nm、2nm追求的就是“性能和功耗的平衡”。而且由于底层技术难度大,这次带头下场的厂家,可能也不是一个国家、一个企业。

铁头作为一个外行,也斗胆给大家聊聊全球参与的“2nm技术战”。

一、裤腰带的艺术

很多媒体报道2nm时,都会很简单的搬运厂家的宣传文档:同功耗下我们性能好;同性能下我们功耗低;我们晶体管塞得多,面积大,堆料丰富……

这也难怪,大家买的是手机电脑,不是芯片里的晶体管,知道“性能好还省电”就行。但是铁头觉得设备性能的进步,是技术发展的结果。所以咱就从外行的角度聊一下,芯片制程上去之后,技术是怎么升级的。如有错误,还望海涵。

首先,铁头要问一个问题,为啥最近几年,宣传自己高性能的芯片总是热得烫手?

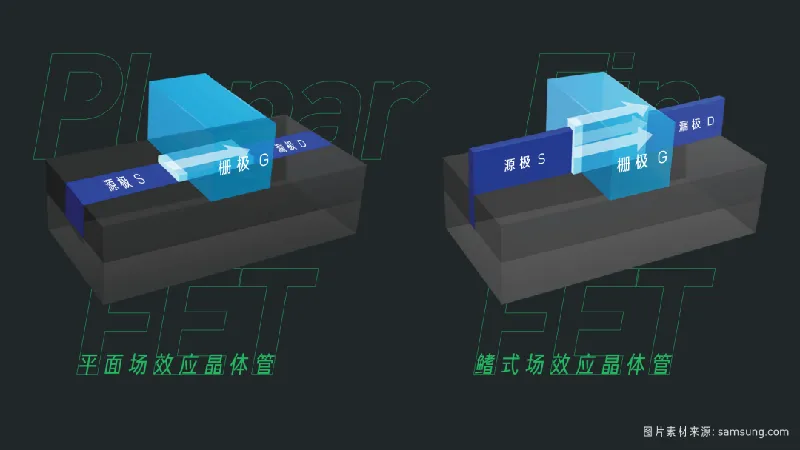

那我们就得看芯片里面晶体管的结构了,芯片里面的晶体管,是场效应晶体管。有一个源极(Source)、一个漏极(Drain)和一个栅极(Gate)。

电流从源极到漏极,形成了计算回路。栅极就要控制电流,让电流按照设计完成计算。

铁头想了半天,最后认为栅极就是个裤腰带。人穿衣服出门,衣服可以跟随身体自由活动,但是裤腰带要把裤子限制住,不然就会掉裤子光屁股。栅极的作用更复杂,但是原理差不多。

芯片越做越精密,塞下的晶体管越来越多。地方不够了,栅极就会越变越细。衣服上的裤腰带变细了,就更容易松,就得经常提裤子。放到芯片里,栅极太细,电流也会不听话,有了自己的想法,这就是漏电。

芯片漏出来的电,没有别的地方去,就会变成热量消耗掉。乱上加乱的是,温度越高,漏电电流还会上升。漏电和高温相互“帮忙”,左脚踩右脚上天。芯片越来越烫,手机就成了暖宝宝。

上个世纪90年代,整个半导体行业都在为发热问题发愁,甚至认为做到25nm就是极限了。

这个时候,有个叫胡正明的华人教授就说:要不然,我们换个裤腰带试试?

他的想法是,把源极和漏极“凸出来”,让栅极包围住它们俩,增加栅极的接触面积。这就像是把需要自己打结的裤腰带,变成了有弹性的松紧带。“主动”贴合身体,把裤子“固定住”,这不就舒服了吗?

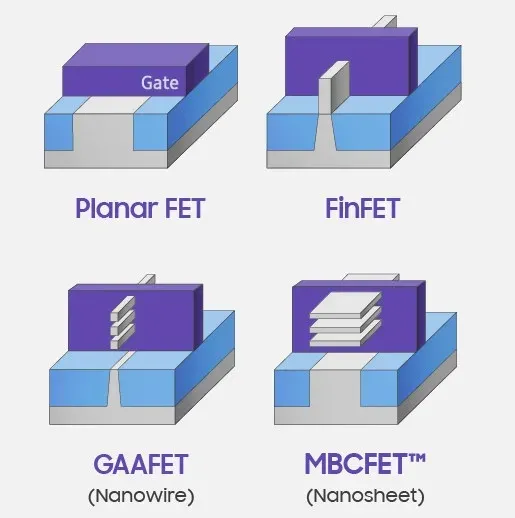

这个结构,看起来就是一个大鱼鳍。所以叫“鳍式场效应晶体管”,也就是FinFET。有了这个技术,才有了后来的14nm,10nm和7nm。

不过这个技术,距离新闻里的2nm还差得远。

二、三星VS台积电:光放话不打架

为啥说FinFET没法做2nm呢?因为这个技术5nm的时候就撑不住了。

之前说了,晶体管的栅极需要防漏电。既然防止漏电,理论上应该是各个方向都不放过。但是FinFET是三方围堵,不是四面环绕。芯片做小了之后,栅极也会变细变小,还是很难限制电流。

为了芯片性能提升,FinFET里面的鳍片数量会下降,这样的话,晶体管驱动电流又会下降,影响性能升级。简单来说,“松紧带”太细太松,穿裤子的人还不敢剧烈运动,因为时间长了还要“掉裤子”。

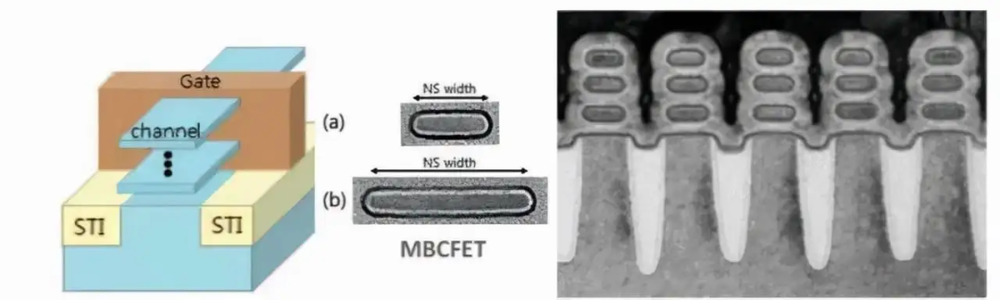

但是三星和台积电还是要做3nm的,那就要把结构继续升级,把栅极和漏极彻底包裹住,就成了全环栅晶体管(GAAFET)。栅极四面都裹上了,可不就是“全环栅”吗?

如果从显微图上看,这个版本的“裤腰带”,就变成了“带扣皮带”,控制能力更强。但是好手艺往往费人力,这种晶体管要加工的是纳米片,细节上的工艺不好调整。而且由于加工精度高,产品的良率也会下降。

看到这里,铁头也就理解为啥三星不放出3nm的具体时间表,明白台积电为啥在5nm和4nm之间纠结了。人在愤怒的情况下,什么都可能做,就是做不出来数学题,还有芯片。

不过台积电准备的,是2nm芯片,纳米片晶体管(MBCFET)的技术,也还是要看后续的发展。按照魏哲家的说法,台积电的2nm着重于测试载具的设计与实作、光罩制作、以及硅试产。

台积电业务发展副总裁Kevin Zhang表示,CFET只是选项之一,具体生产时间不确定。而且3nm会成为拥有大量需求的长节点,对计算能效有更高要求的客户可以率先转向2nm。翻译出来就是:这两年台积电的目标是3nm,2nm是试着玩的,大家不要想太多。

聊2nm,不能把三星忘了。面对“裤腰带问题”,三星在2021年和IBM提出了很激进的思路:竖着放。根据他们的介绍,传统的CMOS是横向构建的,他们换了个思路,垂直放置。所以叫“垂直输送纳米片”。以前大家都横着系裤腰带,我穿背带裤,就不用考虑“掉裤子”了。

从市场的角度看,VTFET还是离我们太遥远。三星现在关注的还是3nm比较多,很早就使用了MBCFET晶体管。只不过到现在为止,三星放出来的还是时间表和PPT,更加详细的技术解析资料还是比较少,所以还是不能太认真。

以铁头对三星面板技术投入的观察,三星在先期技术路线上的选择是很激进的,抢到先进技术,就要砸大量的资源占山为王。三星在OLED领域当时就是引进日本技术后重金投入,最后砸出了个QD-OLED。这种决心不可小视。

但是三星的良率一直是个问题,之前三星的旗舰移动处理器Exynos 2200就是雷声大雨点小,甚至还有紧急撤销宣发的情况。如果三星内部的力量还不能有效整合,2nm也可能会虎头蛇尾。

三、诸侯争霸,三家称王

既然说是“全球2nm技术战”了,铁头就再聊聊美国、日本和欧洲的情况。

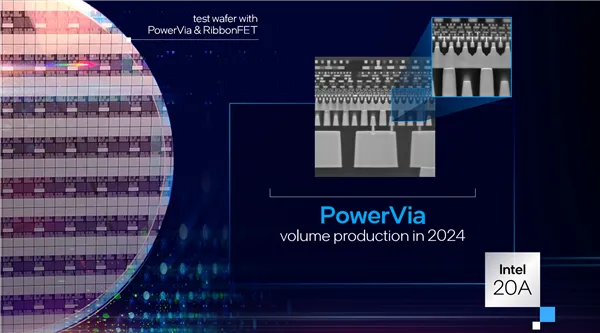

美国方面,目前英特尔公布的路线图显示,2024年Intel 20A(对标行业的2nm)将会问世,对应的技术叫做“RibbonFET”。首先,这个预期要比台积电2025年的目标提前一年。其次,英特尔的计划是一年实现一个技术节点,要比台积电和三星激进。

铁头对比了一下三星和台积电的进程,发现三星和台积电的节点是2023年实现3nm商用。如果今年年底英特尔能放出自己的4nm工艺。说明英特尔的预定计划已经阶段性完成,会对台积电和三星造成不小的压力。

日本目前在芯片制造产能上,依旧是“白嫖”状态。目前可以确定的新闻是,日美签署了半导体合作基本原则,“最早在2025财年启动国内2纳米半导体制造基地”。

铁头含蓄一点说,这个时间实际已经慢了。因为“启动制造基地”说明修建产线还要花时间,与此同时,之前提到的台积电、三星和英特尔产能已经铺好了。至于日媒长期以来宣称的“半导体上游主导论”,实际也影响不到先进制程。造芯片是能力问题,和有没有原料无关。

欧洲方面,目前可以确定的消息是,英特尔会在欧洲投资800亿建设先进制程工厂,大概率今年开工。欧盟也推进过处理器研发的联合项目,但是2nm的研发预算是……1.1亿美元。结合欧洲半导体企业的主体业务看,欧盟目前还没有一个“带头冲锋”的2nm项目,还需要一年的观察,如果这一年做不出什么,以后也做不出啥了。

不过可以肯定的是,今年年底会是一个关键时间点。虽然台积电刘德音股东大会上才放话,表示“对于日美合作2nm,三星以及英特尔在2纳米技术上的发展,台积电并不会特别担心。”但是2nm时代的技术大战,现在已经拉开序幕了。

本文来自微信公众号:科工力量 (ID:guanchacaijing),作者:铁头哥