扫码打开虎嗅APP

本文来自微信公众号:差评 (ID:chaping321),作者:差评君,原文标题:《下周宣布量产3nm工艺,三星这次要狠狠地踢台积电的屁股了?》,题图来自:视觉中国

三星半导体这几年,小日子过的有些不顺。

别的不说,差友摸摸自己的手机,看看三星晶圆厂代工的高通骁龙 888、 8Gen1 ,简直可以说是冬天的暖手宝,夏日的烫手山芋。

好不容易代工出来的产品成了人人喊打的 “ 过街老鼠 ” ,而且芯片生产的良品率也不行。

甚至就连三星自己都心头纳闷啊,事后回过味来,你说为啥我自个的芯片工艺,良品率会这么差呢?

这不,上上上上个月展开了调查,结果到现在也还没个说法。

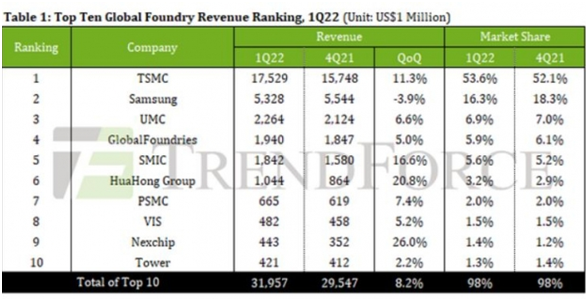

而且作为全球十大半导体公司,在大家都在喊着缺芯缺芯的时候,三星反而成了唯一一个第一季度收入下降的公司。

看着上头的台积电,羡慕的脸都要绿了。

所以说,当年这能造相机,能造手机,能做系统,也能做芯片的三星,这几年到底遭了什么降头?

手机行业吃了鳖,面板行业被国内厂商逐渐挑战,放弃了自家的芯片架构,就连世界上唯二能量产 5nm 以下工艺的芯片代工行业,都被大家嫌弃得如此之惨?

作为一家传承多年的公司,三星这几年拉跨的表现可以说和内斗脱不了关系。

这几年下来,我们也能刷到不少这类三星新闻,包括什么良品率不足欺上瞒下啊,什么论资排辈,部门之间还互相嫌弃......咱能想到的、想不到的内斗方式,三星可能都已经尝试过了。

这把三星太子急的, 2021 年 8 月李在镕 “ 为国 ” 出狱后,还没三个月,公司内部就来了一波不小的人事调整。

三星移动部门,三星消费电子和设备解决方案部门的三位 CEO 都被撤下,还将前两个部门合并成为了新部门 SET 。

又过了一段时间,李在镕还把之前闪存开发部门的领导宋在赫,调到了半导体研发部门担任最新的负责人,派半导体设备解决方案部门的全球制造与基础设施副总裁南锡宇,来出任晶圆代工制造技术中心负责人。

把过去这两位在内存领域搏杀的大将给派到晶圆代工领域,三星这图谋半导体之心,可以说是非常明显了。

毕竟,如果再和过去一样内斗会是什么结果,已经很明显了。

比良品率下降更恐怖的,就是让先进制程的买家失去信心。

高通和英伟达,在这里扮演的就是三星的大买家角色。

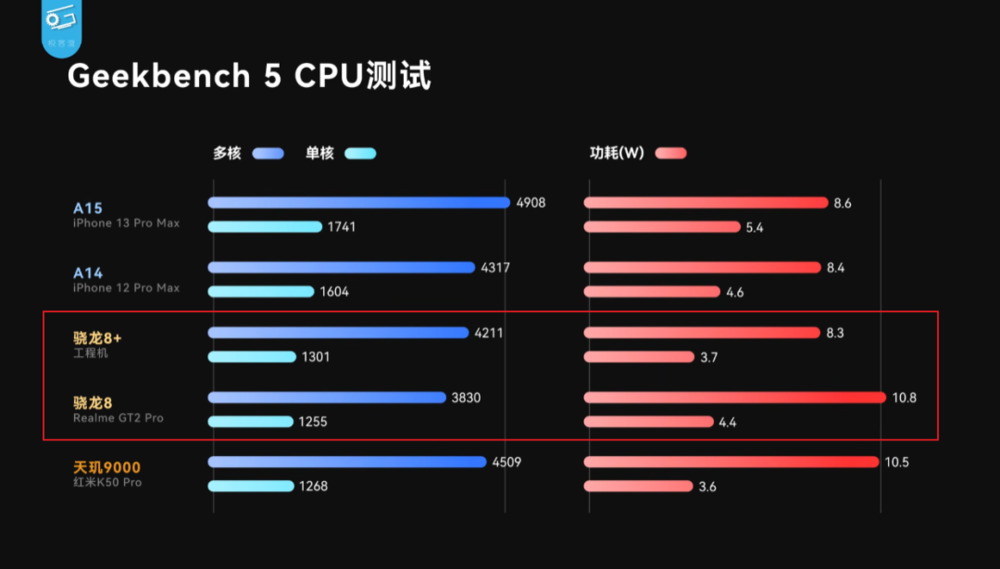

然而如今这俩一个已经跟台积电合作,紧急推出了 8+Gen1 来应对今年联发科的崛起,一个宣布下一代 40 系列游戏显卡也会基于台积电的 N4 工艺开发。

图源:wccftech

不久之前也有媒体拿到了 8+Gen1 的工程机测了一下,和之前三星代工的 8Gen1 相比呢......也就性能高了一点,功耗更低了一些。

这属实是撞车不可怕,谁差谁尴尬了。

图源极客湾

差评君还听到一个芯片行业地狱笑话:

过去大家做芯片呢,是一手交钱,一手按消耗的晶圆数量来给你生产,各家有各家的良品率,能做出多少芯片全凭良品率来摸奖,大家相安无事好多年。

而到了三星这边,因为良品率实在不好恭维。所以它们变成了按照最后实际能生产出多少芯片来计算。

一手交钱,一手交芯片。

的确是让三星自个儿都纳闷为啥良品率这么差了。

当然,芯片工艺,败也技术,成也技术。

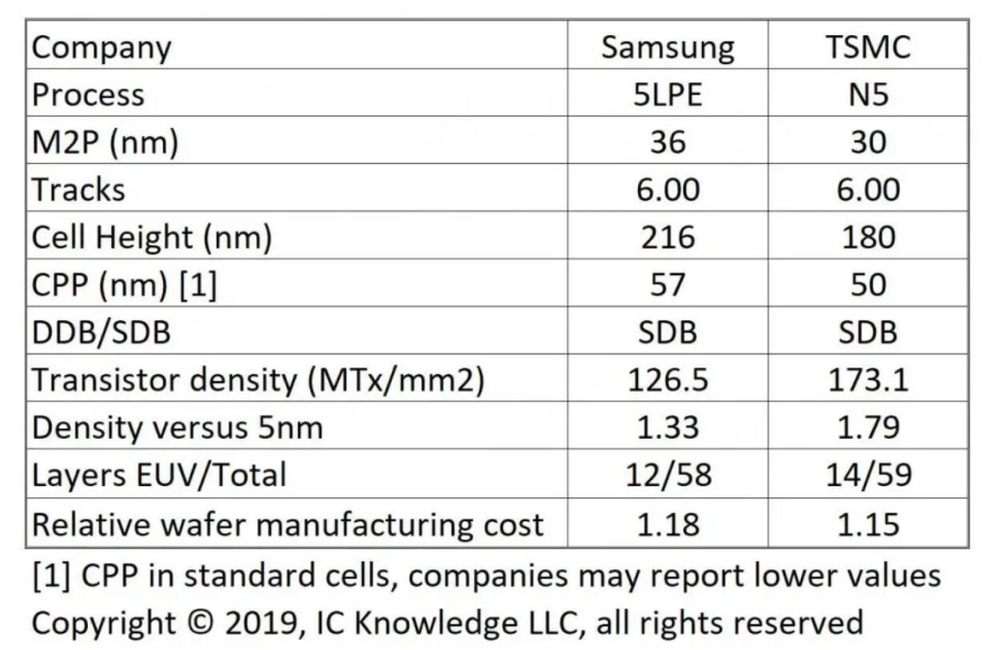

毕竟现在 5nm、4nm 的名称,更多还是厂商用来宣传自己的工艺节点的一种叫法,而并没有绝对的物理意义指代。

为啥三星现在这么尴尬,很大程度上就是因为最新的芯片造得不如隔壁台积电好,良品率、功耗、晶体管密度都干不过别人。

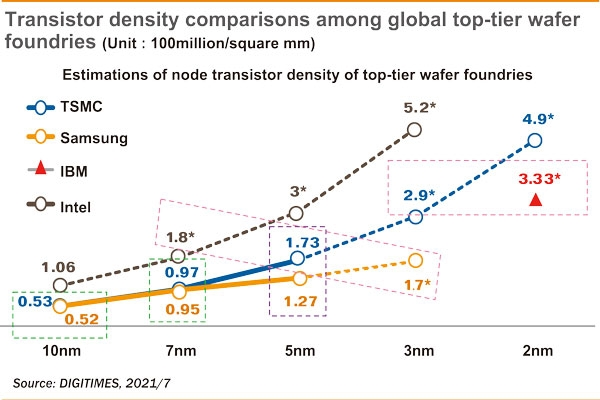

各家工艺密度图,来源:Digtimes

所以,如果下回三星造的芯片良品率更好,功耗更低,晶体管密度更优秀,那这些烦人的问题不就都解决了吗。

巧了,三星也是这么想的,而它们押注未来的,就是 3nm 技术。

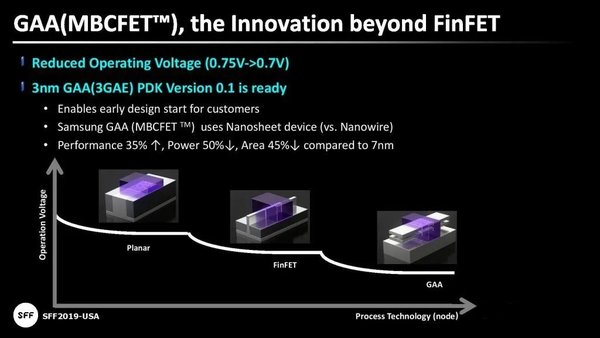

三星,将是世界上第一个迈入 GAA 结构的晶圆厂。

GAA 是啥?简单来讲,它很可能是我们手机 SoC 上会采用的下一代晶体管技术。

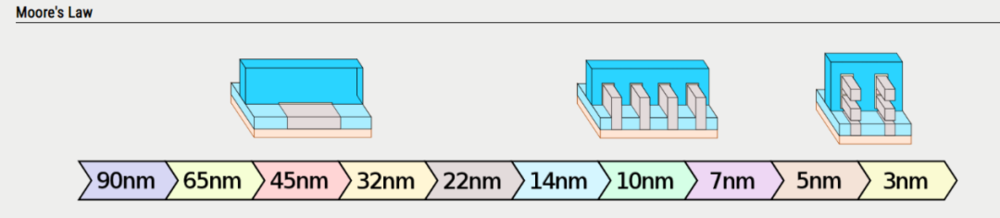

这几年, 随着摩尔定律的演变,芯片越做越小了,晶体管的功耗也越来越低,但是随着晶体管越来越小吧,新的问题——漏电也如期而至。

随着芯片设计进入纳米领域之后,静态功耗的漏电问题就开始翻车。

打个比方,如果把晶体管看作一个 “ 开关 ” ,那漏电问题就像是这个开关没接通,但是还会存在漏电流。

这就是 “ 短沟道效应 ” ,想要减少它带来的漏电功耗,就需要找到新的结构或者新的材料。

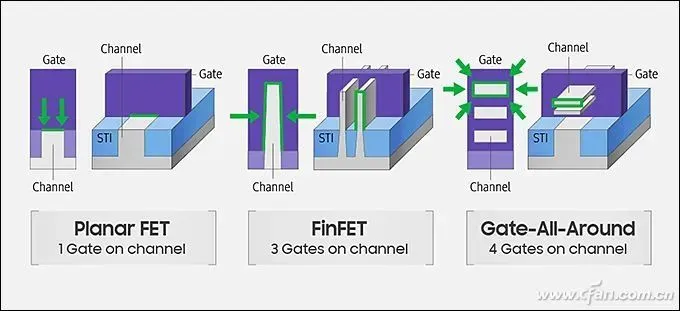

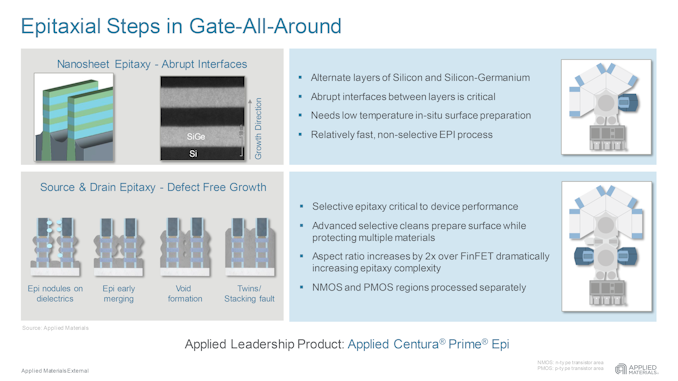

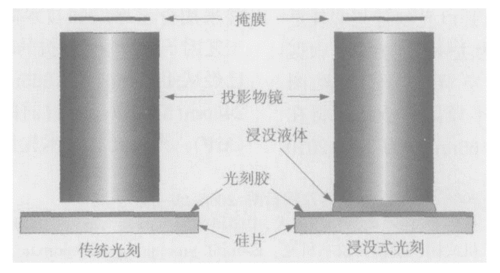

在把芯片做到 22nm 之后,大家采用的技术叫做 FinFET ( 鳍式场效应晶体管 )。

通过 “ 嵌入 ” 的方式增大接触面积,来获得更好的漏电控制性能,有点像把之前一维的晶体管做成二维。

而如今芯片越来越小,做到 3nm 的门槛上, FinFET 也不太够用了。

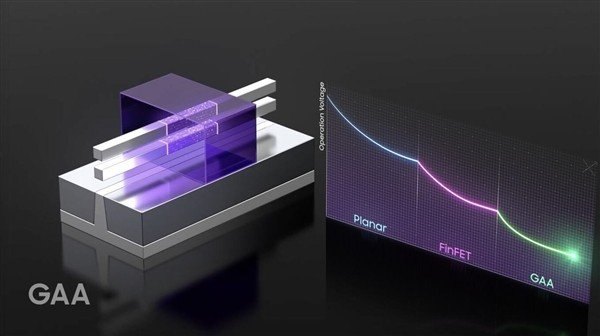

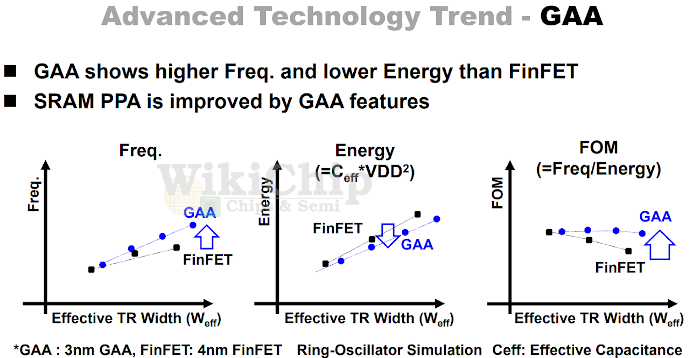

而这回,大家伙倒腾出来解决问题的未来新工艺,叫做 GAA ( 全环栅晶体管 )。

这个就有点像二维变成了三维, FinFET 时的三面环绕变成了四面环绕,这样才能对蠢蠢欲动的电子一网打尽。

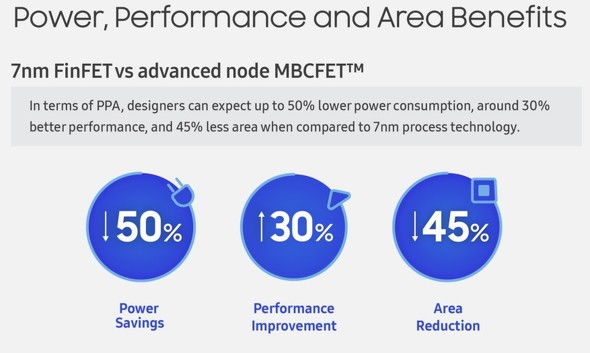

根据三星的报道,和自家的7nm 工艺相比,自家 GAA 的初始版本 3GAE ( 3nm Gate-All _ Around Early )可以减少 35% 的芯片面积,提高 30% 的性能,降低 50% 的功耗。

这饼看着挺香啊,提升 30% 的性能,降低 50% 的功耗,有这提升,啥火龙不得乖乖躺下,给咱们变成冰龙。

欸不是,等等等等,你咋是和 2017 年量产的 7nm 工艺来比 3nm 的,为啥不用明显更接近的 4nm ?

好吧,其实是三星也给了 3nm 和 4nm 工艺的技术对比,但是等于没有完全给。

对比图的的确确是给了一张,但是吧,也只有这一张,这横纵坐标的标尺呢,比较的起始单位又是多少?

你倒是告诉我强了多少啊?

作为在 GAA 领域 “ 第一个吃螃蟹的人 ” 咱能理解三星会面临不少的技术挑战。

但是你看看三星计划要量产 3nm 的时间哈,2022 年第二季度。

本来自家的 5nm 和 4nm 相比台积电就有些注水,在晶体管密度上就有些落后。

不知道三星这算不算 “ 赶鸭子上架 ” 整出来的初代的 GAA,能否和台积电的高密度成熟 FinFET 来竞争,可能还得打个问号。

在过去,新工艺迭代节点的第一批产品,也出现过实际体验的性能反而比不过上一代工艺增强节点产品的情况。( 比如英特尔 10nm 和 14++ )

除开两家公司技术路线的不同,三星想要在 3nm 或者 2nm 阶段实现对台积电的反击,还得过光刻机这一关。

在这方面,台积电和 ASML 可以说是有深厚的革命战友友谊。

20 年前的 ASML 在光刻领域还是名不见经传,靠的就是和台积电的深度合作,在对的时间遇到了对的人。

两家公司一起携手发展 193nm 浸润式光刻技术,把曾经的光刻机巨头尼康给赶了出去。

从 20 年前的 45nm 到前些年的 7nm 工艺,靠的都是浸润式光刻技术。

三星可不像台积电有这层关系,只得看着光刻机眼红,另寻它法。

你看出狱没多久,刚整治完内部的李在镕,上周前往欧洲诸国,别的地方没多停留,直接就跑到荷兰去,跟 ASML 的高层与荷兰的总理谈笑风生。

这一切的目的,都是为了最新的 EUV ( 极紫外光 )光刻机。

总的来说,三星虽然如今在 5nm、4nm 的市场失去了先机,但也不代表着它完全失去了反击的机会。

毕竟,芯片行业是个竞争异常紧凑的市场,曾经的头牌如果走错一步,可能就会在下一代工艺里失去领先的优势。

万一台积电的 3nm FinFET,如果真的因为控制不住功耗翻车了呢?

“ 王权没有永恒 ” ,在这个行业里,领头羊走岔路可谓是家常便饭。

过去, 14nm 工艺门后的英特尔是如此;现在, 7nm 门前的三星也是如此;未来,在 3nm 门槛上依旧坚持选择用 FinFET 的台积电可能也如此。

但无论如何,把翻身的机会寄希望于别人翻车,是不靠谱的。

2022 年的 Q2 已经过了一半多,现在留给三星的时间已经不多了。

参考资料:

http://www.techweb.com.cn/world/2022-06-21/2895108.shtml

https://www.sohu.com/a/509195424_532736

https://www.wealth.com.tw/articles/62a4772b-212e-4382-91d3-b208c8a59162

https://ieeexplore.ieee.org/document/9601158

https://www.sohu.com/a/529794330_121011018

https://www.eet-china.com/news/202203241027.html

https://en.wikichip.org/

本文来自微信公众号:差评 (ID:chaping321),作者:差评君