扫码打开虎嗅APP

本文来自微信公众号:中国电子报(ID:cena1984),作者:许子皓,编辑:连晓东,原文标题:《2纳米之战》,头图来自:视觉中国

1月13日,台积电CEO魏哲家表示,2022年70%~80%的资本预算将用于2纳米、3纳米等先进工艺技术的研发。此前,老对手三星也表示将于2025年量产2纳米。去年,英特尔调整了技术路线,大踏步向2纳米进军,而IBM展示的2纳米工艺制程也着实让人惊艳了一阵子。新年伊始, 2纳米作为阶段性制高点,吹响了芯片先进制程之战的号角。

一、台积电与三星的战争

目前,在先进工艺这一赛道上,玩家只剩下了台积电、三星、英特尔和IBM。现在最先进的制程工艺当属初露锋芒的4纳米了,而能达到此项工艺技术水平的,全球也只有台积电和三星两家。根据此前台积电和三星放出的消息,2022年将成为3纳米的诞生之年,并且都表现出了将在2025年量产2纳米的决心。虽然3纳米现在还没被达到量产,但从几大厂商在3纳米上的研发进度就可初见端倪。

台积电(南京)有限公司总经理罗镇球曾公开表示,台积电正在用新工艺证明了,摩尔定律仍在持续往前推进。作为先进工艺的推动者,台积电2018年推出7纳米,2020年推出5纳米, 2022年将会如期推出3纳米,而且2纳米工艺也在顺利研发。

据台积电官方资料显示,台积电的3纳米相比上一代的5纳米工艺,在逻辑密度上提升了1.7倍,性能提升了11%,同等性能下功耗可降低25%~30%。台积电将在2纳米节点推出Nanosheet/Nanowire的晶体管架构并采用新的材料,在性能、功耗和密度也将进一步提升。

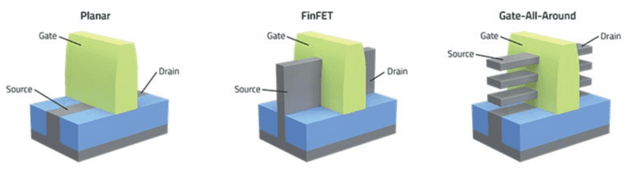

赛迪顾问集成电路产业研究中心高级分析师杨俊刚向《中国电子报》表示,台积电将会在2纳米芯片中采用GAAFET工艺,目前来看台积电已经试产了3纳米芯片,预计今年将会量产,但是台积电3纳米的工艺现在还是采用FinFET工艺,从研发到生产上,FinFET转到GAAFET还需要有一定的适应调节能力。

平面晶体管与FinFET以及GAA FET示意图

资料来源:LamResearch

“从质量和产量两方面考虑,台积电无疑会率先推出2纳米代工工艺,目前台积电投资约300亿美金的Fab20正在建设,预计2024开始运营,主要负责3/2/1纳米先进工艺,2025年2纳米将在这里最早实现量产。”芯谋研究高级分析师张彬磊笃定的向《中国电子报》记者表示。

三星作为台积电最强有力的对手,近几年的发展速度飞快,并且多次公开表示要在芯片加工领域与台积电展开竞争,全球敢这么叫板台积电的也就只有三星了。在IEDM 2021 国际电子元件大会上,三星更是携手IBM宣布了一种名为垂直传输场效应晶体管(VTFET)的芯片设计技术,并表示该技术突破了目前1纳米工艺设计的瓶颈。

2021年10月,三星宣布3纳米芯片已经开始成功流片,将于2022年上半年开始生产,2纳米芯片将于2025年量产,并且3纳米工艺就将会采用GAA工艺,2纳米技术将会持续采用GAA工艺,在3纳米进军2纳米工艺的技术节点上将会节省一些步骤。

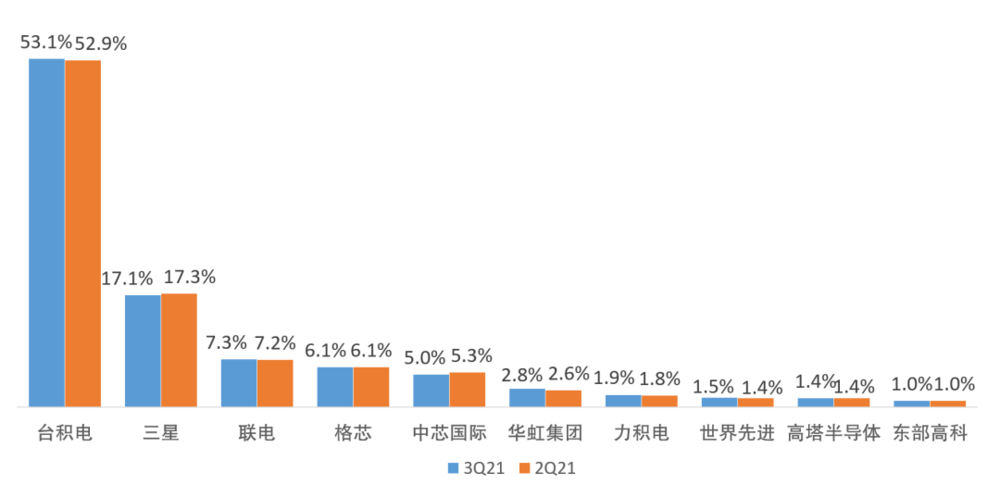

TrendForce:2021第三季全球前十晶圆代工企业市场份额占比排名

尽管三星的进步很大,但与台积电的差距仍然很大——市场研究公司TrendForce的报告中显示,2021第三季,三星代工销售额相较于第二季度增长11.0%至48.1亿美元,市场份额却从2020年的17.3%下降到17.1%。而台积电第三季度占比53.1%,比第二季度的52.9% 增加了0.2个百分点。杨俊刚认为,原因在于台积电在晶圆代工领域积累了丰富的客户资源,包括苹果、华为、高通、英伟达等。而且先进工艺技术快速且稳定,对于苹果、华为、高通等追求先进制程迭代速率较快的企业,产品更早进入市场,会为自身带来一定的市场优势。产能方面,台积电的晶圆代工产能领先三星于三倍之多,在产能使用和保障上,规模更大的厂商会更有优势。其次,台积电属于纯晶圆代工厂,而三星是一个IDM企业,自身生产的产品和一些纯IC设计厂商的产品具有竞争关系,客户也会在挑选代工厂商上有所考虑。

张彬磊从产品品质方面指出,按照以往的经验来看,三星在晶体管参数、芯片功耗、发热问题、良品率上都比台积电略逊一筹。特别是采用三星制程的芯片始终摆脱不了严重过热问题,性能也低于台积电所代工的芯片,使得三星很难扩大市场占有率。

二、英特尔、IBM左右逢源

英特尔“牙膏厂”的名号在外甚是响亮,原因就在于研发进度过慢,工艺停留在7纳米的时间过长,像是在挤牙膏一样,不少人怀疑英特尔黔驴技穷了。但最近英特尔像是突然意识到了危机感一样,到处求合作,此前和三星、IBM签署了联合开发协议,共同研发2纳米制造工艺,而现在又传出要与台积电合作,可以说是左右逢源。

杨俊刚表示,英特尔在去年7月份的工艺和封装大会上,公布了英特尔最新的技术路线,首先把重要工艺命名进行了修改10纳米技术改名Intel 7,7纳米技术改为Intel4,5纳米技术改成Intel 3,2纳米技术改成Intel20A,Intel20A工艺也是开始由FinFET工艺转向了GAA晶体管,其中将会采用两项RibbonFET、PowerVia技术。其中RibbonFET技术是英特尔自FinFET技术以来推的首个技术。并且英特尔表示将会寻求和台积电合作,双方共同加强对2纳米工艺技术的研发。

而老将IBM为我们带来的最大的惊喜就是在2021年5月发布的全球首个2纳米制造工艺,并在纽约州奥尔巴尼的工厂展示了2纳米工艺生产的完整300mm晶圆。据预计,IBM 2nm工艺或能在每平方毫米芯片上集成3.33亿个晶体管。相比之下,台积电5nm工艺每平方毫米约为1.71亿个晶体管,三星5nm工艺每平方毫米约为1.27亿个晶体管。这使得2nm芯片的性能有望提升45%、功耗有望降低75%。

“此款2纳米芯片,并未实现真正产业化,采用了GAA工艺,使2纳米的晶体管密度达到了333.33(MTr/mm2),高于目前所已知的其他芯片制造的工艺的晶体管密度。”杨俊刚介绍到。但张彬磊认为,这种实验室工艺,与量产工艺差距很大。IBM和英特尔应该把目标放在5纳米以上的工艺。

三、2纳米要过三道坎儿

想要研发出2纳米芯片,所需要的环节非常繁多且缺一不可,就像我们在做手工时,都需要拥有合适且优秀的材料、熟练且完善的技术和先进且趁手的工具,在先进制程的研发中更是如此,其中晶体管架构方式的转变和优化就是技术的象征。

对于2纳米的研发来说,新型材料的选择与应用一样会起到至关重要的作用。乔安表示,半导体制程已逐渐逼近物理极限,因此晶体管架构的改变、新兴材料的应用、亦或是封装技术的演进都会是芯片持续提高效能、降低功耗的关键。

中国科学院院士张跃指出,硅基集成电路制程与制造技术经历了数十年的发展,特别是在高端芯片领域已经形成了完整的产业链与技术链。近年来,二维材料及其范德华异质结电子学器件已经在超低功耗晶体管、超快逻辑运算、光电互联以及新型高密度存储等领域表现出巨大的发展潜力。

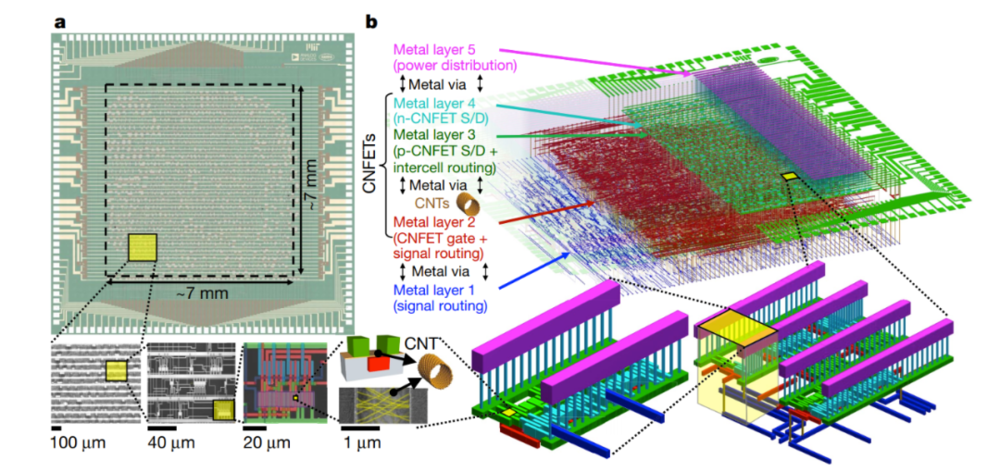

碳纳米管基芯片

资料来源:Nature,2019,Vol.572,Page586

二维材料和一维材料是未来突破2纳米以下先进制程研发的潜力材料。石墨烯、碳纳米管、过渡金属化合物等二维或一维材料的尺寸较小,是未来有望替代硅基的新材料。目前碳纳米管基芯片及石墨烯芯片已经有国际研发机构成功实现小规模的研发实验,未来通过中试和量产后,有望突破硅基材料难以延续摩尔定律的困境。赛迪顾问集成电路中心高级咨询顾问池宪念向《中国电子报》记者表示。

目前,2纳米制程技术关注的重点在于晶体管架构将由FinFET正式进入GAAFET世代,相较于FinFET,GAAFET架构为四面环绕式包覆,更能有效提高效能同时控制漏电(降低功耗);TSMC在2纳米将正式导入GAAFET,而Samsung2纳米制程将为其第二代GAAFET架构制程,预期整体稳定性及效能都将更加提升。TrendForce集邦咨询分析师乔安表示。

从目前的各个大厂公布的技术来看,GAA(Gate-All-Around)FET全栅场效应晶体管技术将会成为2纳米芯片研制的主流工艺,GAAFET工艺采用的是纳米线沟道设计。沟道整个外轮廓都被栅极完美包裹,对沟道的控制能力会更好,并且拥有更好的静电特性,尺寸能够进一步微缩。

最后是硬件设备是否足够先进可以支撑2纳米的制造,自然就是指光刻机,而现有的光刻机是否已经满足2纳米的开发需求了呢?

张彬磊认为,当前的光刻机支持2纳米工艺研发完全没有问题,5纳米量产工艺的光刻机使用多层曝光工艺就可以实现。但是考虑到成本,量产需要的光刻机目前ASML还在开发中。

目前已量产的光刻机还不能满足2纳米的开发需求。据公开信息,荷兰ASML公司正在研发High NA(高数值孔径)EUV光刻机,可满足2纳米的研发和生产需求。首台High NA EUV光刻机将于2023年开放早期测试,并从2025年开始量产。但具体来看,满足2纳米制程生产需求的光刻机还需要突破光学分辨率的问题,道阻且长。同时,为适应2纳米的开发需求,光刻胶也需要进行进一步的革新以满足光刻机更高分辨率的需求。

四、2纳米之后

尽管现在处于后摩尔时代中,但2纳米的研发已经慢慢出现了轮廓,但是否还会向1纳米发展,甚至进入埃米时代,先进工艺的发展历程是否还会稳步发展下去。

目前来看,除了少数需要超大算力或者存储容量且对芯片体积、能耗极为敏感的领域,1纳米及以上的成熟工艺几乎已经完全可以满足民用类芯片的所有需求。除非在新的通信技术加持下推出需要超大算力、存储容量的爆款应用产品,否则很难让普通消费者为手机支付较大开支,来进一步大幅提升性能。众所周知,先进工艺代工价格非常昂贵,民用芯片一是考虑性能,二就是价格。

乔安表示,根据目前先进制程领导厂商台积电、三星及英特尔所发布的制程路径图观察,先进制程的发展仍然在持续进行。然而如同上述,在半导体制程逐渐逼近物理极限的趋势下,晶体管架构的改变、新兴材料的应用、亦或是封装技术的演进都会是摩尔定律延续下去的重点。

先进工艺肯定会遭遇物理瓶颈,摩尔定律也肯定面临失效风险,后摩尔时代的重点将不会聚焦在无限制提升工艺制程上面,而是通过先进封装、Chiplet、优化芯片架构,甚至提升软件层面的算法,来提升芯片的运算效率,在这些领域,可供提升的空间还很大,创道投资咨询总经理步日欣向《中国电子报》记者表示。

本文来自微信公众号:中国电子报(ID:cena1984),作者:许子皓